Hi,

Could you clarify the input type of the UCC21732? Also, can I drive the PWM inputs at 3.3V while the Vcc is powered via 5V?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

Could you clarify the input type of the UCC21732? Also, can I drive the PWM inputs at 3.3V while the Vcc is powered via 5V?

Hi,

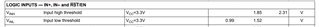

UCC21732 is a CMOS input gate driver. It has an inverting input (IN-) and a non-inverting input(IN+). The gate driver output will only go HIGH when IN+ = HIGH and IN- = LOW. The gate driver output will remain LOW for any other combination. You can either short IN- to GND and only feed a PWM signal to IN+ to operate the driver, or if you're using two driver to drive a half bridge you can use both IN- and IN+ to provide interlock (prevent both driver to be ON at the same time) by connecting both PWM signals coming from the MCU as shown in Figure 8-2 PWM Interlock for a Half Bridge in the UCC21732 datasheet. Interlock function is explained in section 8.2.2.2 PWM Interlock of IN+ and IN- (link here).

This gate driver input thresholds are directly proportional to the power supply applied to VCC. If using VCC = 5V, must use 5V logic on other pins as well.

Best regards,

Andy Robles

Hi Jimmy,

Andy has given detailed information about how the PWM signals to be planned to get the device functional.

Just one additional information: The datasheet spec for VinH and VinL are based on the VCC supply.

So Vinh threshold is 0.7* of VCC

Similarly Vinl threshold is 0.3* of VCC

For reliable operation. So when VCC=5V, planning INP=3.5 or greater is needed. hope it helps.

thanks

Sasi