hello

I have a question about the P876411A5RQKRQ1 used for the J721S2 PDN.

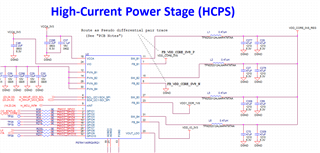

I am trying to tie Buck 1,2,3,4 together and use them as High-Current.

Is the voltage fixed at 0.8V? Or do I need to program it?

I understand that P876411A5RQKRQ1 FB1~2 is connected to VDD_CORE_0V8_REG in J721S2 EVB schematic.

I don't understand why FB3 is connected to VDD1_DDR_1V8 and FB4 is connected to VDD_IO_3V3.

Is there any reason?

Also, I don't want to use GPIOs, but leave the pin floating?

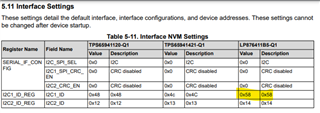

Also, I need to know the slave address to use I2C, but I don't see anything in the datasheet to set the slave address.