Hello Team,

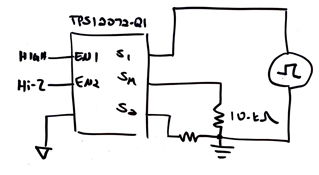

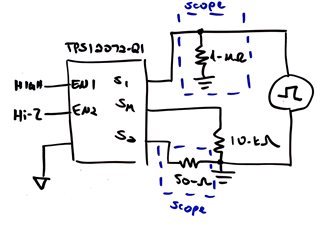

We are planning to use the device TPSI2072 for one of our applications.

The device is used for muxing some 12V signals.

The input will be connected to the SM pin of the device and S1 will be connected to one device and S2 will be connected to another device.

EN1 and EN2 will be used to select the signal flow.

When EN1 is high and EN2 is low, the signal will flow from the SM pin to the S1 pin and to the end device.

similarly for EN2.

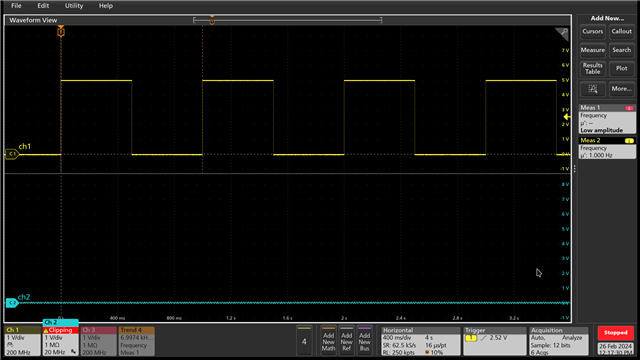

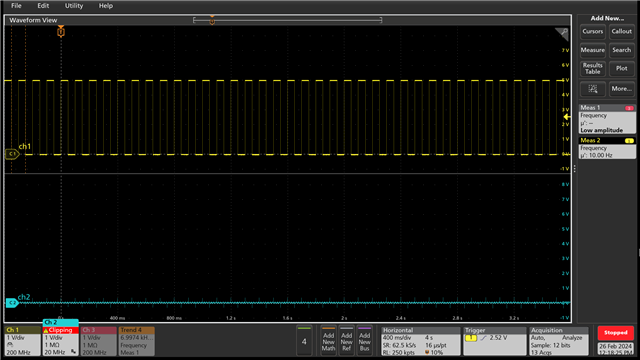

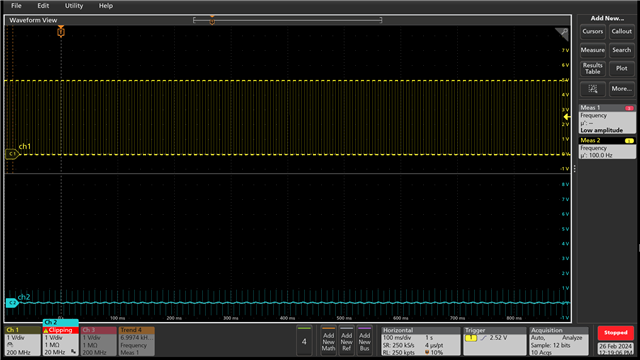

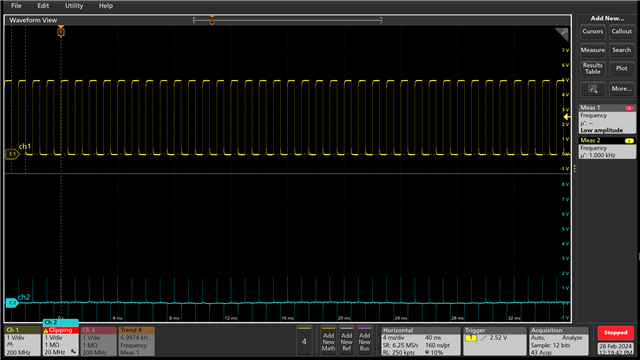

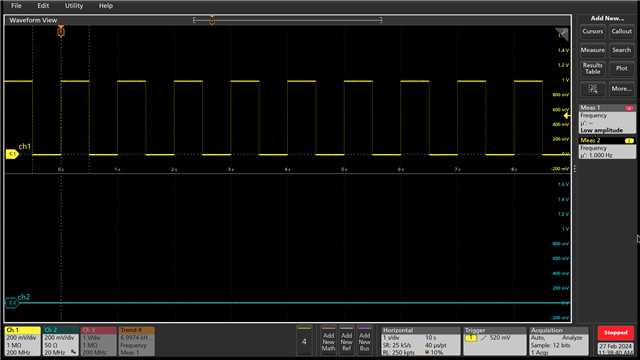

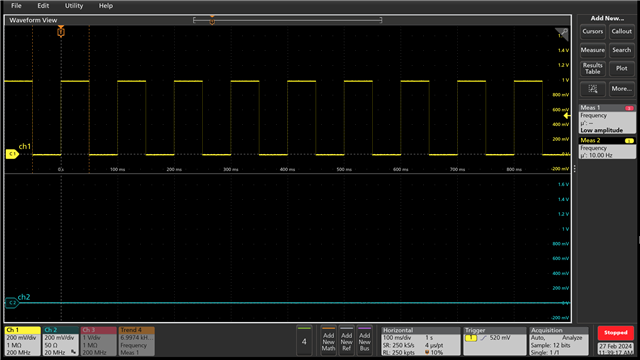

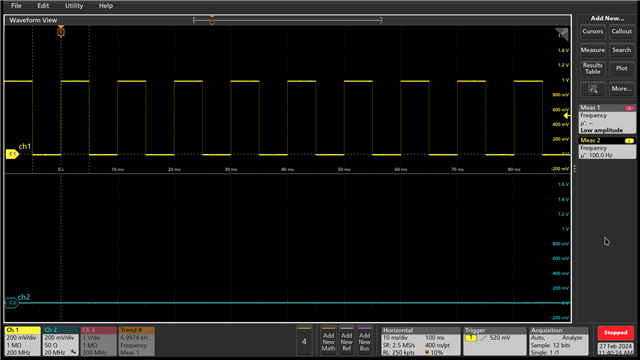

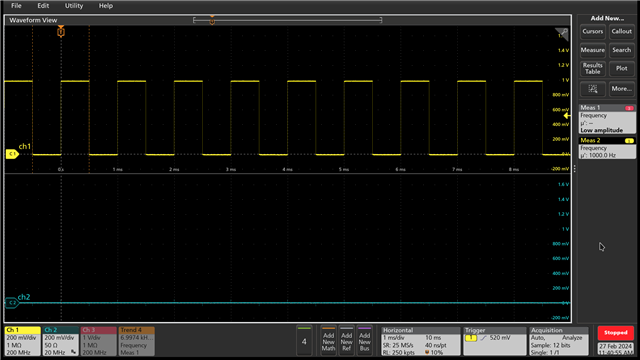

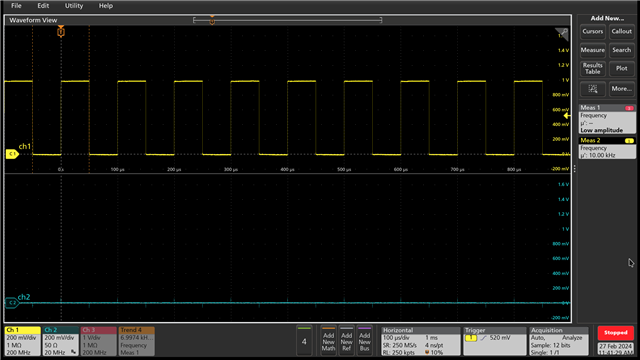

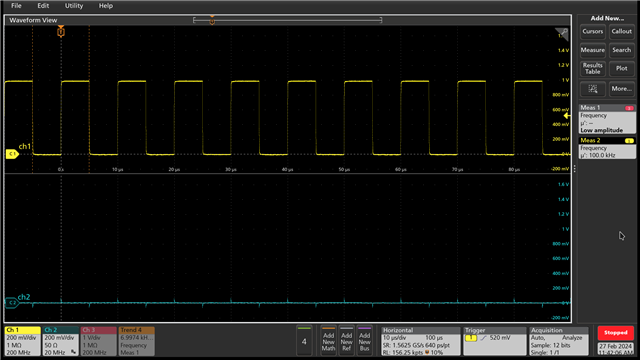

When high frequency signal is fed at the SM pin, is there any possibility the signal could be present at the S2 pin even if only the EN1 is selected (due to the parasitic capacitance of the MOSFET)?

Looking for your reply.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.