Other Parts Discussed in Thread: CSD18540Q5B, CSD19505KTT, LM9061-Q1

Hello Team,A.

We want to select an N channel based on the following specifications.

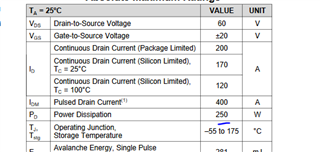

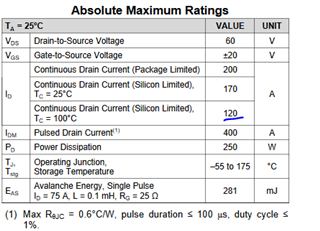

90A continuous current

200A pulse (100uS)

150A pulse (1mS)

Low RDSon

Low input and output capacitance

The MOSFET is used to turn on/off the power to a board (48V system).

Can I use the MOSFET CSD18542KTT for our application?

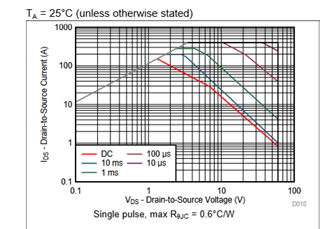

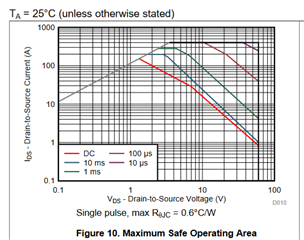

How is the VDS related in SOA.

The above graph shows a DC drain current of more than 120A when VDS is above 1V.

The VDS is the product of RDS and te drain current

The RDS of the device is 3.3-mΩ and the ID is 90A.

So the VDS will be only 297mV.

Please correct me is I am wrong.

Can anyone check whether the device is working in SOA or not?

Looking for your reply