Hi,

in designing a Class-D audio amplifier I encounter a topic which I do not understand.

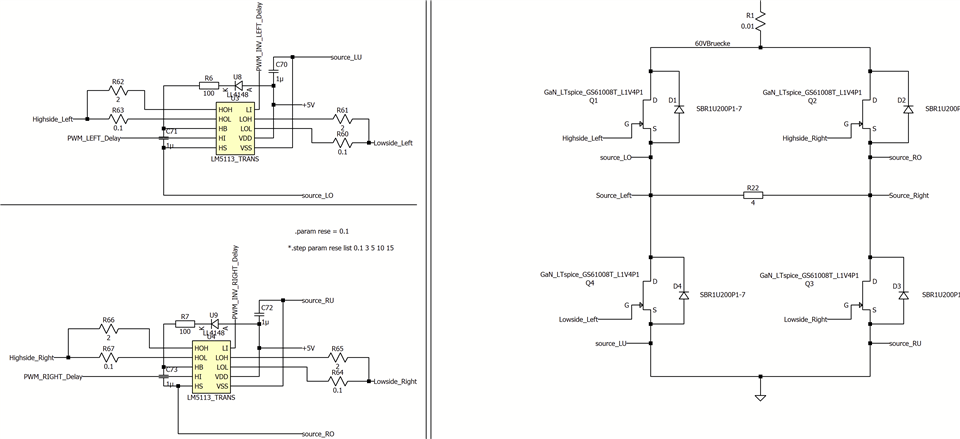

The circuit depicted below has been simplified for debugging reasons. The input signals for the LM5113 (PWM_LEFT_Delay and PWM_INV_LEFT_Delay) are 50% duty cycle 5V signals with a frequency of 500kHz. In order to prevent a cross current in a half bridge, they have a dead time of 20ns.

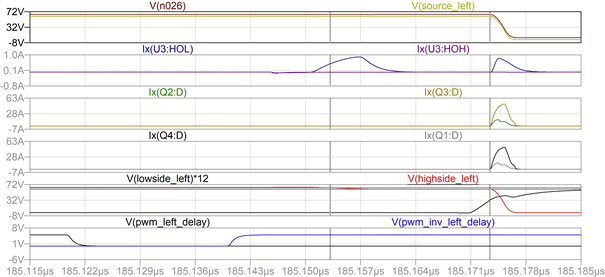

In the simulation however there is not really a dead time when the gate signal of a high side switch (Highside_Left) falls. For approximately 20ns, Highside_Left will fall by only 4.8V (the value, the gate signal is above supply voltage during boost). Only when the time comes that the gate signal of the low side switch (Lowside_Left) rises, Highside_Left will finally fall to zero. It can be seen, that the HOL pin of the LM5113 delivers current in two phases: first, when Highside_Left falls by 4.8V and then once again when it falls to zero. Obviously HOL is floating during the 20ns in between. As a consequence a cross current is flowing beween the high side switch and the low side switch (despite of the dead time in the LM5113 activation signals).

Could you help me to understand and fix this topic?

Best regards

Helmut