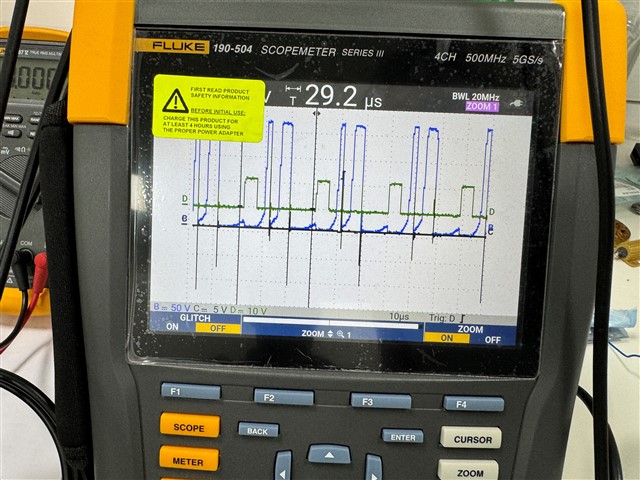

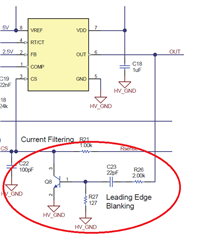

Hi, iam using UCC28C45-Q1 for flyback design, but my pwm pulses are skipping and also cs pin is picking noise even after using RC filter with lower cutoff frequency. Also is there any issue if we use ic ground and power ground as same.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.