Other Parts Discussed in Thread: TPS65988, , TIDA-050014, TPS65987, TPD4S311A, TPD6S300A

Dear TI,

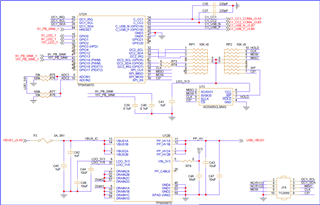

Supporting a large production run consuming a lot of TPS65988 we designed a production test fixture that leverages the TIDA-050014 reference design to negotiate 9 and 15V profiles from our TPS65988 based device under test. The block diagram attached shows a simplified concept where the processor on the DUT is using a port expander to 'press' the 5V, 9V and 15V buttons on the TI Sink board (TIDA-050014) and overall this concept works pretty well. Recently we've had a failure in the test board that's require replacement of the TPS65987D chip and a few weeks later that circuit failed again. It happens to be sink #16 on the test board. We're updating the test board now to correct a few issues and we've recalled the test board with the failed TPS65987D to investigate. The board arrives tomorrow AM and I'm going to connect the Aardvark and try to debug the damaged circuit. I'm looking for any input you have as to what I can test to determine root cause and I will send you additional information after I have the board in hand and can probe it for physical defects.

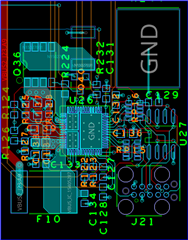

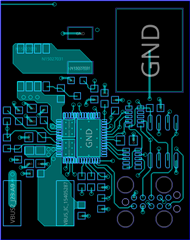

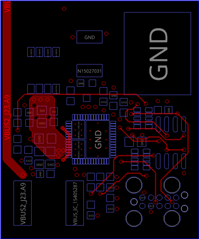

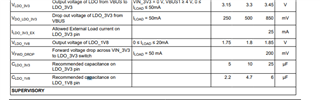

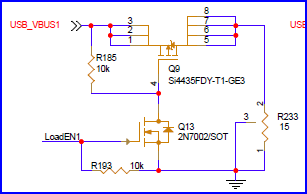

The timing of the test is not overly fast - we allow a few seconds at each voltage and we also connect a small load (a 15 ohm resistor) during test. Both ends should support 3A, and at most we're puling 1A during test. The snip pasted below shows 1 of the sixteen test channels, followed by the majority share of the load circuit which is quite simple and also controlled by a port expander. TI already has an old copy of our product schematic but I can provide that to you offline if you would like, just ask and provide me your email address. I can also provide the full schematic for the test board if that's helpful.

I'm hoping that in response to this you can offer some specific registers to check, specific tests I can perform, or direct guidance on what to pull form the Application Customization Tool. Once i have the board I plan on pulling a full debug snapshot and will provide that in addition to any other failure indications I find during visual or electrical inspection. Those should be loaded here tomorrow - and I would also highlight any requested info you may want to see.

Thanks!

Adam

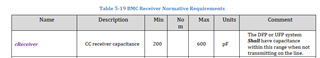

TPS65987D: Single channel sink circuit. There are sixteen in total.

Port expanders used to press TIDA 050014 buttons and read back the feedback LED states

Single circuit's load. 15 ohm power resistor with body tied to ground.

Attached (simplified) block diagram: