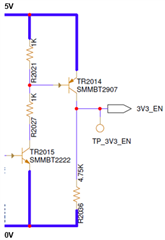

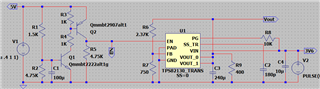

Can you provide the TPS82130 EN input circuit schematic? I am looking at a TPS82130 circuit that generates 3.3V where VIN = 3.6V and the EN input is provided by the circuit below. I am trying to work out why its EN signal 3V3_EN is sitting at approx. 2.3V and whether the TPS82130 device has been damaged because the EN input voltage may have exceeded it absolute maximum rating of VIN + 0.3V and it then being pulled down to 2.3V.