Other Parts Discussed in Thread: TPS7H1111EVM-CVAL

Hi,

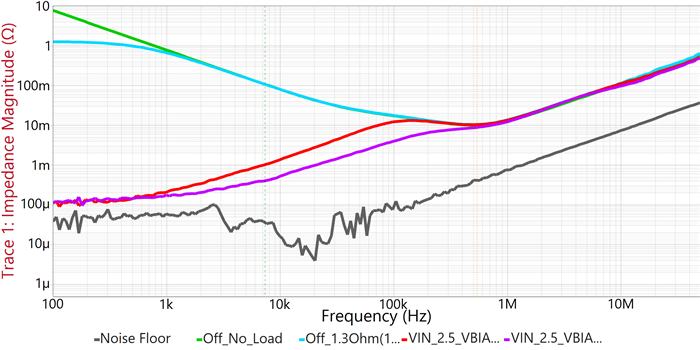

Is there any output impedance data for the TPS7H1111-SP?

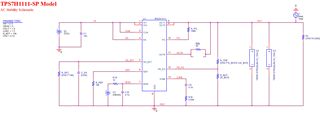

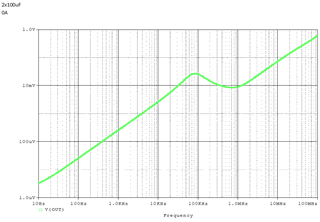

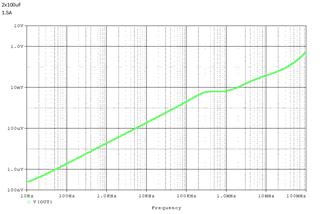

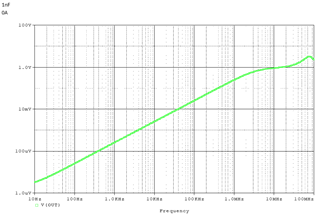

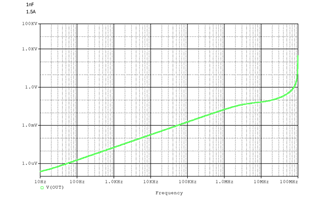

I've simulated the output impedance at 0A and 1.5A using 2x100uF output caps and also simulated with a 1nF cap.

How does the simulation match up to the data?