Other Parts Discussed in Thread: TPS7H5001EVM-CVAL

Hello,

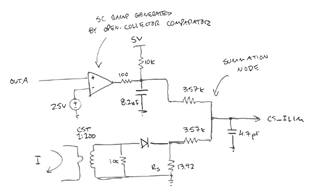

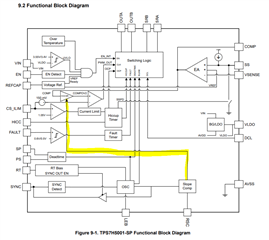

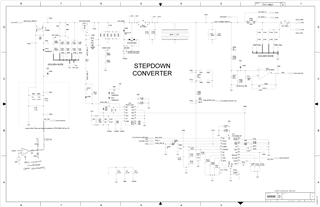

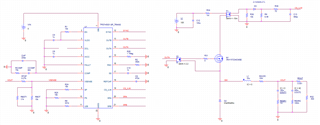

I am currently testing using this PWM in a Buck Converter design. In my design, I have chosen to include slope compensation on top of the current signal external to the PWM chip. I've done this because I would like slope compensation included even when the current limit is encountered.

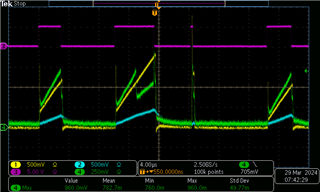

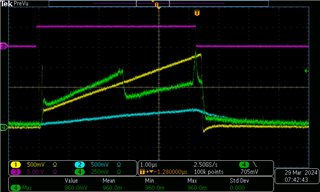

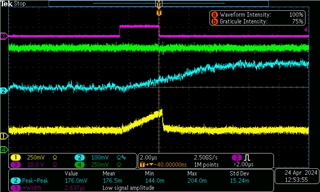

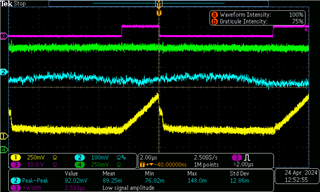

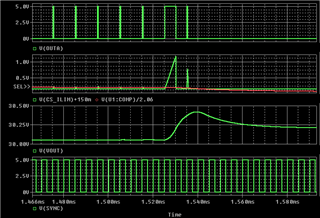

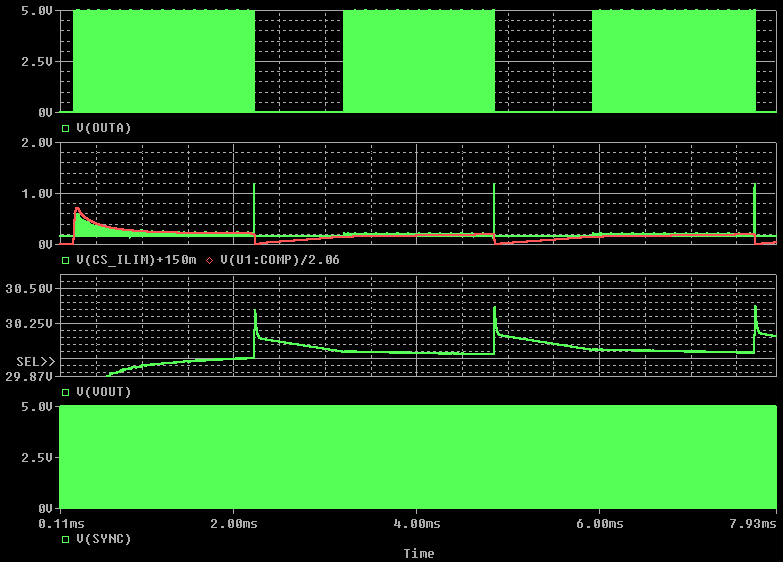

Even though I have included (what should be) sufficient slope compensation to the current signal before it enters the chip, I see subharmonic oscillations at duty cycles near 50%, and see what appears to intermittent, sharp dips in impedance at the CS_ILIM pin (in green, where the current sum waveform has rectangular "bites" taken out of it).

I have tried a range of RSC values for the internal slope compensation, ranging from almost no slope compensation (as none should actually be required, RSC=10M) up to approximately 2x m (.068V/us, RSC=562k).

I always seem to get at least a little subharmonic oscillation accompanied by the weird voltage dip at CS_ILIM (for DC near 50%)

Any light you can shed on this is appreciated. Thanks,

CHAD

Below:

CH1 YELLOW: CST output (prior to summation)

CH2 BLUE: Slope Compensation Ramp (prior to summation)

CH3 MAGENTA: OUTA

CH4 GREEN: CS_ILIM signal (1:1,50% summation of CST and CS Ramp)