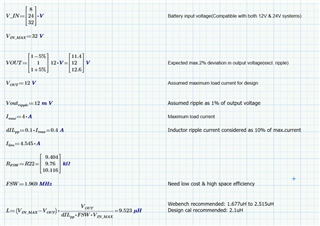

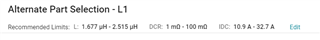

While performing WCCA, I've noticed that the calculated inductor(9.6uH-> Even at nominal values) is far less than the recommended value from both webench & excel calculator(max.2.5uH). Added the webench report here for your reference.

WBDesign35_Current limit 4.54A_1.8uH.pdf

WBDesign35_Current limit 4.54A_1.8uH.pdf

Also, webench is mandatorily keeping one electrolytic capacitor at the input side(even though it's of low value-> <20uF). I was thinking to replace it with multiple ceramic capacitors as it provides better rms handling capacitor & low ESR value. Is it because of capacitance change due to bias voltage in ceramic? The battery will be kept atleast 1m from the actual PCB and we have load dump & EMI filter before this buck boost circuitry.