Other Parts Discussed in Thread: LM5148

Hi,

A follow up question on previous post.

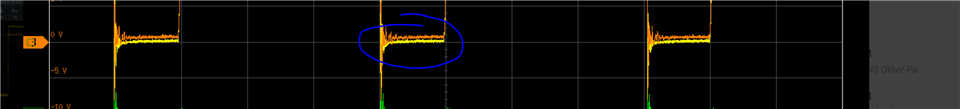

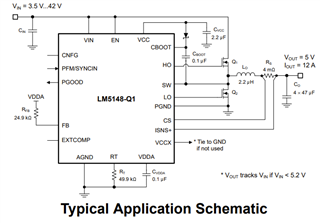

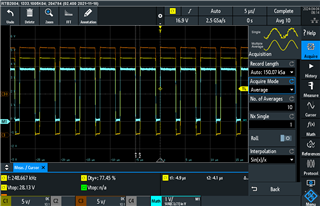

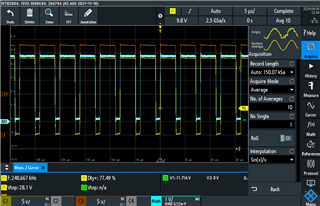

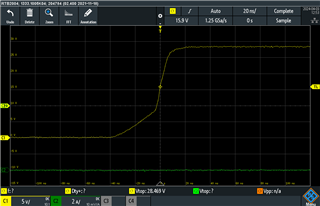

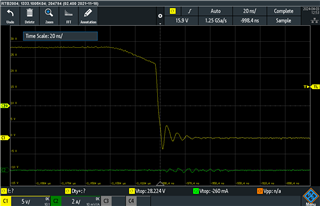

I have attached the below two pictures just to hear if anybody can confirm if these look OK. They show the switch node (SW) rising and falling edge. Input is 28V and the output is not loaded. It runs with a frequency of 250kHz.

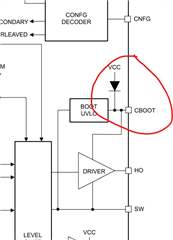

I measured the HO output togehter with the SW node. Yellow trace is HO and orange SW. I came to notice that the difference voltage is only 3.66V which seems a little low to fully turn ON the top MOSFET?

Thank you