Other Parts Discussed in Thread: LM25180, , LM5180

Hello TI team,

I need to implement a PSR flyback converter using the LM25180QNGURQ1 with the following parameters:

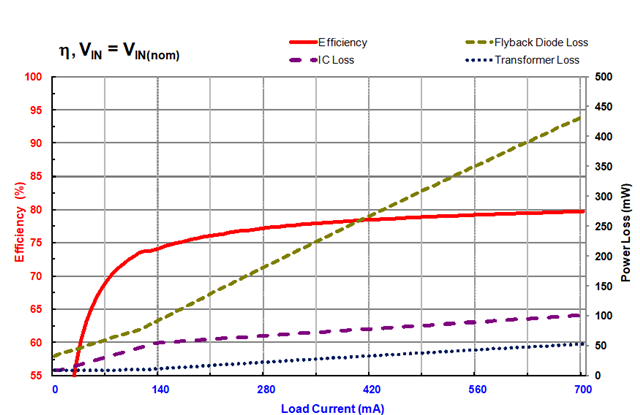

Input voltage range: 9-36VDC

Input threshold: 8.5V On, 7V Off

Output voltage: 3.3V

Rated load current: 0.7A

Output voltage regulation: +/-1.5%

Question 1

Why does the WEBENCH tool lead to different component values than the Excel tool?

Question 2

The option to design a CISPR Class 5 input filter is not available in WEBENCH for this converter. Is there an Excel tool or a TI application note available to design this filter?

Question 3

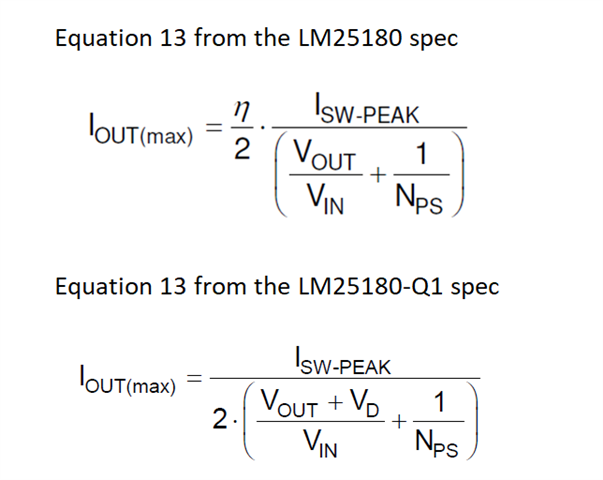

Besides being AEC-Q100 qualified, is there a difference between the LM25180 and LM25180-Q1 IC? Some of the equations used are different from one spec to the other (LM25180 vs LM25180-Q1). As an example, equation-13 calculating Iout(max) is different from one spec to the other (LM25180 vs LM25180-Q1). Equation 13 used in the LM25180-Q1 spec gives a result which is aligned with the Iout(max) provided in the Excel tool. Which spec equation, LM25180 or LM25180-Q1 yields more accurate results for Iout(max)?

Question 4

If the calculation of a transformer ratio leads to a ratio of 2.5:1, does it round up to 3:1 or round down to 2:1? If the calculation gives a transformer ratio of 3:1, but this transformer is not available from any manufacturer, can you change the transformer ratio to 2:1? The spec says that the higher the transformer ratio, the higher the stress on the SW pin of the IC.

Question 5

When calculating the flyback diode in section 8.2.1.2.4, it says “In general, choose a flyback diode with current rating greater than the maximum peak secondary winding current of NPS*IPRI-PK(max)”. For my design, it gives 3x1.5A = 4.5A minimum. Can this current be multiplied by the maximum Duty Cycle factor to lower this current? Indeed, it seems that this current is not continuous at maximum Duty Cycle or short circuit. The maximum DC for this design is around 60% at Vin(min), which gives: 0.6x3x1.5A = 2.7A for maximum diode current. To support this affirmation, WEBENCH recommends a flyback diode of 3A for this design. The example given is section 8.2.1.2.4, also lowers the diode current with the maximum Duty Cycle.

Question 6

Can Low ESR Tantalum capacitors be used for Cout? For some reason, I cannot find any 100uF/6.3V MLCC with soft/flexible terminations. The environment for this design is automotive therefore SMD ceramic capacitors with soft terminations are a must. I do realize that the Capacitor ESR will interfere with the poles of the control loop.

Question 7

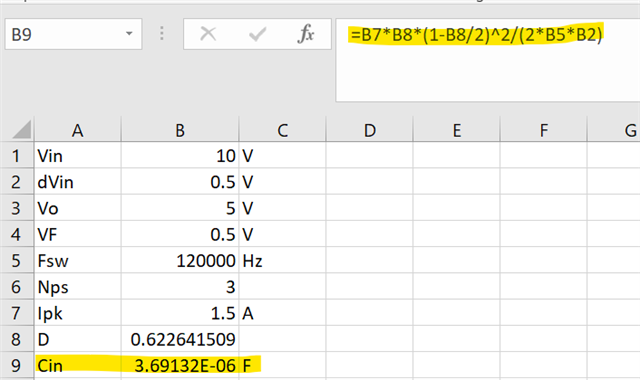

How do you get the result of 2uF for Cin using equation 24 in the example design of section 8.2.1.2.7? No matter how I calculate, I always get 0.35uF as a result. I used equation 4 for IPRI-PK(BCM) to calculate the current.

Question 8

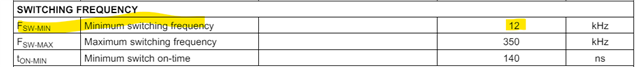

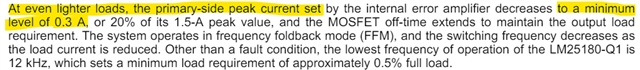

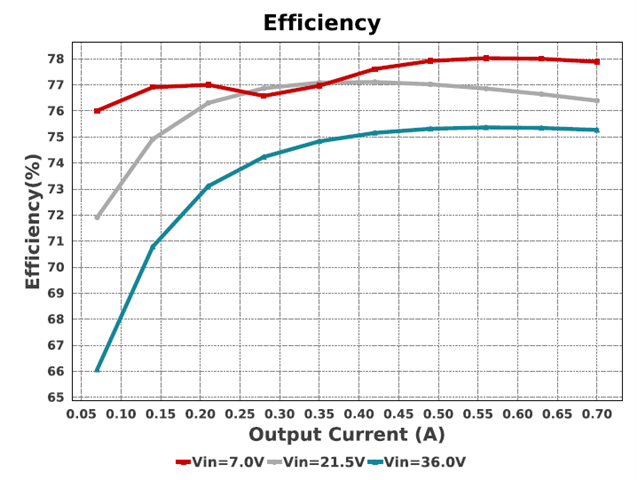

Is there an equation to determine the minimum load required? In the past, I have used the following formula with PSR flyback from other manufacturers: “Lpri x [ISW-PEAK(FFM)] x f(min)/ 2xVout” which leads to around 5mA. LM25180-Q1 spec section 7.3.2 says “Other than a fault condition, the lowest frequency of operation of the LM25180-Q1 is 12KHz, which sets a minimum load requirement of approximately 0.5% full load” gives 0.005x0.88A = 4.4mA. WEBENCH recommends 4.1mA. Which minimum current is correct?

Thank you,

Regards

Eric...