I'm designing a USB 5V powered single cell lipo charging circuit. We want to have I2C communications + interrupt to a 3.0 - 3.3V logic level microntroller to monitor the BQ25628E registers. I understand that in the typical application circuit, VREF is the logic voltage of the host MCU, although that doesn't seem to be explicitly stated in the datasheet.

1. Please could you confirm what VREF is intended to be?

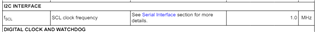

Furthermore, we seek to implement the lowest power circuit, so the host MCU will be entering sleep modes. We plan to power the I2C SDA/SCL and BQ25628E INT pullups with 10k resistors to a GPIO on the MCU, so that the pullup rail can be powered down for lowest power operation.

2. Please can you expand on how much leakage current the I2C and INT pullups are expected to draw with e.g. 10k Ohm resistors to 3.3 V (datasheet gives values for 1.8V) and also advise on the best scheme for lowest leakage / quiescent current in the surrounding / supporting circuitry around the BQ25628E?

3. Would we be better off leaving the I2C and / or INT lines pulled up during low power modes of the MCU for lowest leakage or can they be pulled to ground when the MCU is sleeping?