Tool/software:

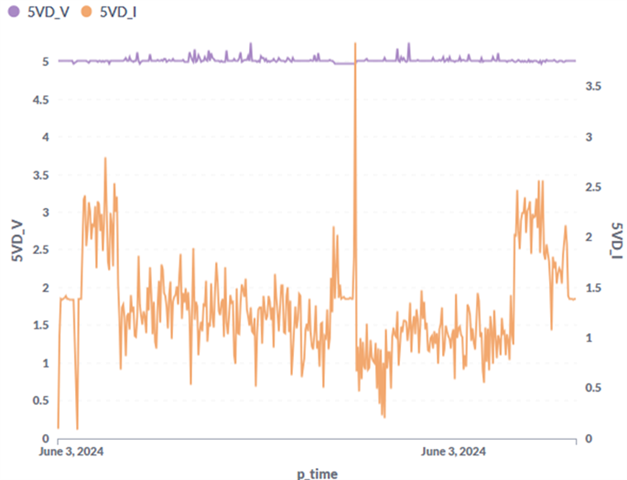

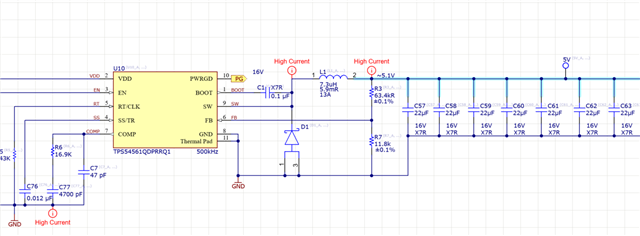

Hi, a quick one on the TPS54561-Q1. My load is a bit noisy and the current can bounce around by a delta of up to 2A in 200-500ms. The regulator handles this pretty well, but I still see a ripple response on the rail of up to +/-400mV and am wondering what is the best part of the design to tune to minimise this essentially transient step response ripple? Many Thanks.