Other Parts Discussed in Thread: BQ79616, UCC23511

Tool/software:

Hey TI Experts,

We are designing a system for Bi-directional current flow to and from a Battery Pack.

Hence, we have the FETs on the high side arranged in back to back topology with Sources of the Discharge and Charge FETs common.

The following are the points in which we require clarity:

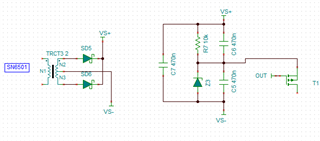

1)In order to drive the gate of the FETs in high side we've used an Opto-coupled Isolated gate driver through which the source terminals are isolated from the logic side.

We've used an isolated power supply specifically for this purpose.

2) We have used a pre-discharge circuit consisting of a P channel FET in series with current limiting resistors. Hence, as the Pre-discharge FET is connected in parallel with the discharge FET and as the P channel FET requires lower potential at gate terminal than source terminal. Thus, we've used another opto-coupled isolated gate driver for achieving the same by referencing gate to ground and source to the PDSG control pin.

We would like to know if the circuit will work optimally or are there any optimizations or changes needed.

Awaiting your valuable response on the same.

Thanks & Regards

Ibrahim