Tool/software:

-

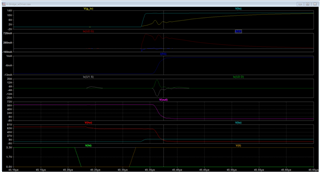

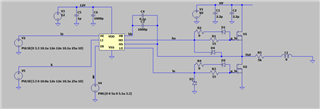

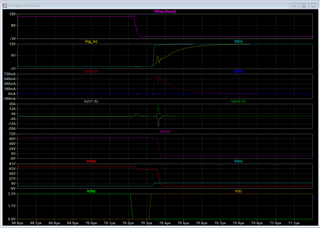

Hi / li are input PWM waveforms to driver

-

Ho / lo are output of the driver

-

Vout is the voltage at the 5k load.

-

U1 is the top FET, U2 is the bottom FET. I have plotted the Source current of U1 and drain

-

I(R5) is the current to the resistive load.

-

Ix(U2:G) is the current into the bottom FET. g_lo is the voltage at the bottom FET gate, lo is the output of the driver (I have the standard resistor in parallel with resistor diode filtering on the gates.