Hi all,

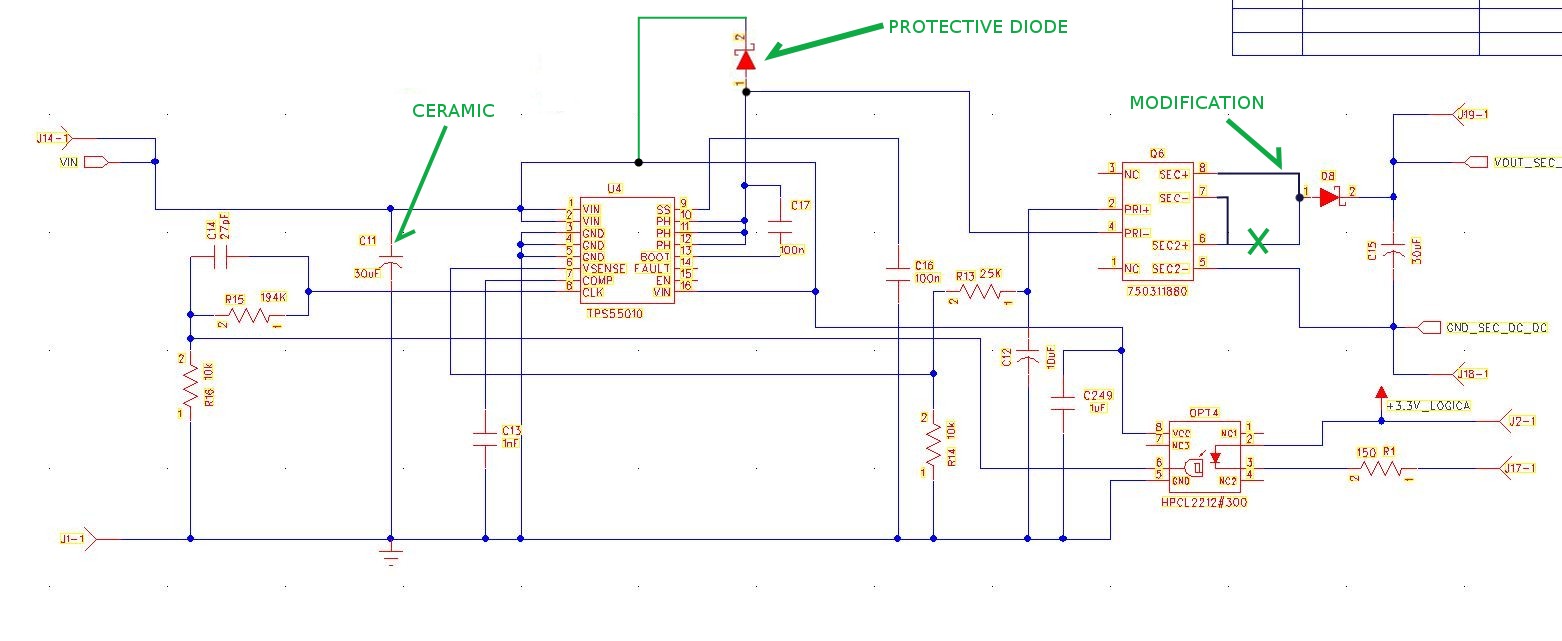

we are testing some samples of TPS55010 and we experienced some problems due to the systematic failure of low side NMOS (?). At the moment we built 7 prototypes and all failed in the same way.

Is there some reason for such instability? We are using the schematic indicated in the datasheet with the magnetic from WURTH 750311880 (also suggested). The PCB looks like the ones indicated in the evaluation board.

The device starts regularly but after a while (e.g. connecting the ground of the DSO to the board) it fails.

Are there some critical issues in the board layout that were not reported in the datasheet?

Any experience?

Gianpietro

Micromed-Italy