Other Parts Discussed in Thread: TIDA-010208

Tool/software:

Hello TI Team,

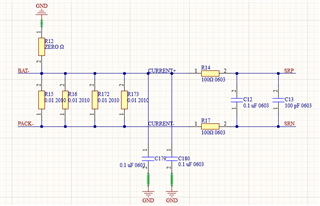

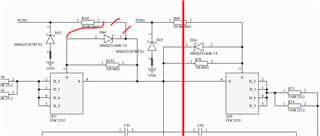

I'm using the BQ76952 as a slave in my BMS, and I want it to support my battery pack configuration. I am using 16 LFP batteries, each with a capacity of 100Ah and a voltage of 3.2V, to create a battery pack with a total voltage of 51.2V and a capacity of 5kWh.

Based on the high-side MOSFET design, could I use the TIDA-010208 reference design? Additionally, could you recommend a current limiter from Texas Instruments to add to my schematics?

Thank you for your assistance.