Other Parts Discussed in Thread: LM7480-Q1, LM74722-Q1, LM74800-Q1

Tool/software:

Hello TI experts,

I want to design a circuit that receives two different power sources as inputs and performs prioritization of the power path to the load.

The first power source is a 55V power supply.

The second power source is a 12-cell battery (42V-50.4V).

I plan to use two ideal diode controllers to control and prioritize the power path (as shown in the article "Six System Architectures With Robust Reverse Battery Protection Using an Ideal Diode Controller" - Design #6).

There is an external controller that sends an "Enable/Disable" signal to the ideal diode controllers to turn the load on and off according to a certain logic.

As long as an "Enable" signal is received in the ideal diode controllers:

The circuit needs to deliver power to the load from the power supply as long as the power supply is connected to the circuit.

Once the power supply is disconnected, the circuit should route the power to the load so it comes from the battery.

When the power supply is reconnected - the circuit has to switch back the power path to the load so that it comes again from the power supply and not from the battery.

Switching must be fast enough to keep the load alive during the change of the power path to the load.

As soon as the "Disable" signal is received in the ideal diode controllers - all the MOSFETs have to close to completely turn off the load.

Note: There is one "Enable\Disable" signal coming from the external controller.

When the "Enable\Disable" signal is sent - both of the ideal diode controllers receive it, so as long as the "Enable" signal is sent, both of the ideal diode controllers receive it at the "EN" pin but prioritization of the power path to the load should be done according to what I described above.

Conceptual scheme of the architecture:

Additional information and questions:

When the system (load) will be fed through the power supply path the continuous current will not exceed 5A (for a long time) but when the system will be fed through the battery path the continuous current will reach approximately 250A (for about 40 seconds).

Because of the high current passing through the path of the battery to the load, I will have to connect to MOSFETs Q3 and Q4 several more MOSFETs in parallel.

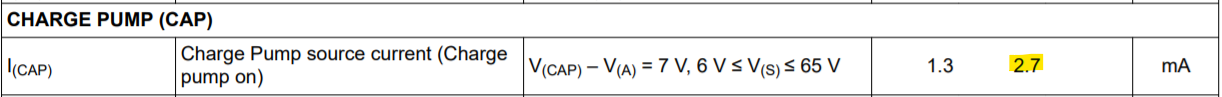

To turn on and off fast enough several MOSFETs that are connected in parallel, I will need a device with the highest gate drive strength.

- I know I can design the circuit with the LM7481-Q1 instead of the LM7480-Q1 shown in the schematic above for higher gate drive strength,

but can the LM74722-Q1 be used in this architecture for even higher gate drive strength?

I did not find any reference design for this type of architecture using LM74722-Q1, I would appreciate it if you could attach a reference design if there is one...

The power path from the power supply to the load is a low current path and the MOSFETs Q1 and Q2 are smaller and do not require parallel connection to additional MOSFETs as is the case with MOSFETs in the power path from the battery to the load.

- Doesn't the difference in MOSFETs between the two paths mean that the battery path MOSFETs turn ON slower than the power supply path MOSFETs turn OFF, causing the system to sense the lack of power source and momentarily turn off while switching between the two power sources?

- Will the situation be as I described? Is there a way to solve this problem?

Another thing:

I don't really need features like OVP \ UVLO \ BATT_MON

I just need to control the ON and OFF state of the system using the "Enable/Disable" command to the ideal diode controllers

And when the ideal diode controllers are "Enable", then the default voltage source will be the power supply, and only when the power supply disconnects does the battery connect to the system (of course fast enough so that the system does not feel the change of the voltage source).

In addition, I also need reverse current protection so that no current flows from the power supply to the battery or from the battery to the power supply.

I would appreciate receiving guidance or some design reference,

are there things that are very essential to implement or things that are unnecessary to implement?

Are there things I should pay attention to when designing the circuit?

Are my requirements from the circuit even feasible?

Any information you can give that will help me design the circuit more correctly would be greatly appreciated

Thank you very much!

Niv