- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi

I have been reviewing the datasheet of the TPS61033DRLR, and I have a question about VIN and VOUT.

In our application, the VOUT is set to be within the range of 4.826V to 5.174V base equation 1 in page 11.

※include ripple and Load Transient

When the input voltage VIN is approximately 5.1V,

could TPS61033DRLR achieving the VOUT range( 4.826V to 5.174V)?

I can not well understand

Pass-through mode when VIN > VOUT

in the 1 Features in page 1.

Thanks and Best Regards

Chunli

Hi Chunli,

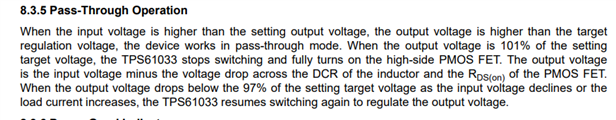

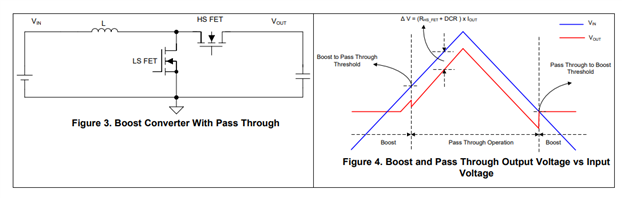

Pass-through mode when VIN > VOUT means the high side FET is always turned on when VIN > VOUT, then VOUT is followed by VIN.

You can refer to 8.3.5 section for more details about this, and also the VOUT at this mode is related to the VIN and the load current now.

Regards,

Nathan

Hi Nathan

Thank you for your quick response.

Do you have any experimental data or Figure?

I want to know the Instantly changing [When the output voltage drops below the 97% of the setting target voltage] or [When the output voltage is 101% of the setting target voltage] about the output voltage of the TPS61033.

[When the output voltage drops below the 97% of the setting target voltage as the input voltage declines or the load current increases, the TPS61033 resumes switching again to regulate the output voltage.]

Thanks and Best Regards

Chunli

Hi Chunli,

Unfortunately we don't have a data about this.

You could refer to this AN about a diagram of Boost converter with pass through, or we suggest to apply for a TPS61033EVM sample to try with a test.

Thanks.

Regards,

Nathan