- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

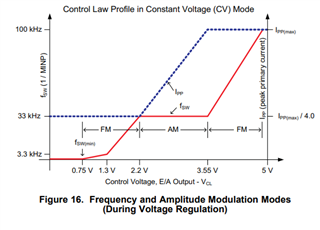

This is an excerpt from the UCC28711 datasheet.

The image implies that once the average output current reaches the regulation reference, the controller transitions to frequency modulation mode to regulate the output. It also states that the voltage is maintained below the regulation target and VDD is kept stable.

Please confirm if my understanding is correct:

Is my understanding correct?

The reason I am asking this question is that in an SMPS rated at 24V/2A, I observe that the VCST value measured at the CS pin remains approximately 700mV, regardless of whether the load is 0.3A or 1.5A.

This behavior seems consistent with the datasheet's description of the controller's operation in frequency modulation mode and the relationship between VCST and Vvs. However, I would like to confirm if this is expected behavior based on the design and regulation mechanism of UCC28711.

Hello,

Please see my comments below.

Regards,

Thank you very much for your thoughtful response. It helped me understand many of the confusing points. However, I still have a few questions:

In your response, I am curious about the parameters used in the equation. I understand that 33kHz corresponds to the frequency in the AM region. What does 44kHz represent?

I measured the CS pin and GND pin of the PWM IC using an oscilloscope with a passive probe, and I observed a value of about 1V in some cases. I assume this measurement might be incorrect due to noise components caused by parasitic inductance. Would this assumption be reasonable? The SMPS is operating stably.

Hello,

1. I made a typo it should have been 33 kHz and not 44 kHz. Sorry about that.

2. If you power supply is stable the measurement may not be correct. You might want to recheck that just to make sure it is correct.

Regards,