Other Parts Discussed in Thread: TIDA-01620

Tool/software:

Dear TI Team,

We have designed a USB-C to DisplayPort adapter board using the TUSB544. While DisplayPort Alternate Mode negotiation appears to complete successfully and the TUSB544 switches the signals as expected, we are encountering a persistent issue: the external monitor stays black most of the time, and briefly displays the image for about 0.5 seconds at random intervals before going black again. Over a period of 10–15 minutes (without touching the board or cables), we typically observe about 5 image flashes.

Here is a summary of our setup and observations:

-

DP Alt Mode negotiation is verified using a Power Delivery analyzer.

-

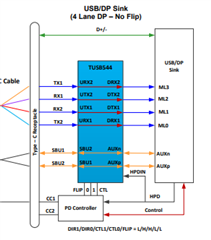

The HPDIN pin is held high (3.3 V). We force it via I²C (register

GENERAL_4, bit 3:HPDIN_OVERRIDE). The HPD pin of the DP connector is connected to HPDIN, and we measure a stable 3.3 V. -

The TUSB544 configuration appears correct — we can read the display's EDID, and when the image is briefly shown, it is clear and of good quality.

-

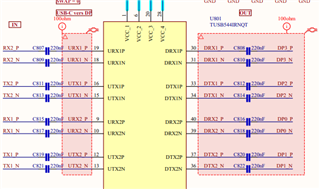

Hardware configuration:

-

30 cm USB-C cable (PD compatible) between the host PC and our board

-

9 cm PCB trace length between the USB-C and DP connectors

-

50 cm DisplayPort cable between the board and the monitor

-

-

Differential pair routing rules followed:

-

100 Ω ±10 % differential impedance

-

Intra-pair skew ≤ 0.127 mm (5 mils)

-

Inter-pair skew ≤ 2.54 mm (100 mils)

-

Clearance between pairs: 3W (3x trace width)

-

Shielding vias placed between differential pairs

-

-

Under Linux (i915 driver), we observe:

-

4 active lanes

-

2.7 Gbps

-

Link status: GOOD

-

-

From the DPCD registers, we confirm for lanes 0–3 (

0x202and0x203):-

CR_DONE = 1 -

CHANNEL_EQ_DONE = 1 -

SYMBOL_LOCKED = 1

-

-

However, we observe very high symbol error counts in

SYMBOL_ERROR_COUNTregisters (0x210to0x217), often showing0xFFor near-maximum values.

We have tested numerous DRX/URX EQ settings, but without significant improvement.

We currently lack access to a high-speed oscilloscope or protocol analyzer capable of eye diagram measurements, which limits our ability to inspect DP signal quality at the physical layer.

With your expertise, could you help us identify the most probable root cause of this issue — namely the brief, random flashes of valid image, with the screen remaining black the rest of the time?

Thank you in advance for your support.

Best regards,

Clément