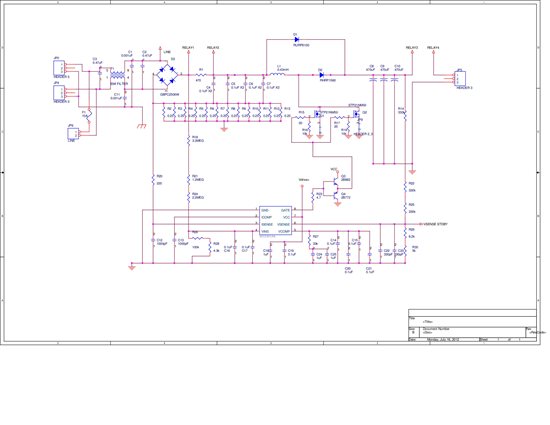

Hello! I am currently designing a PFC circuit using the UCC28019. I havent finished soldering everything into place, but I need to report on some specifics when I get done. These include the switching operation of the IC. I am just wondering which part of the sample circuit governs the ripple voltage? I assume that the gate turns the mosfet switch on (close) when the output voltage (governed by the voltage divider at VSENSE) reaches a certain voltage above the nominal output voltage, and then it turns off (open) when it reaches another threshold below the nominal output voltage. Am I correct in assuming this? If I am, then how are the max and min thresholds adjusted?...

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.