Hi,

We got a question from my customer about TPS2042B-Q1.

Could you help us?

[Question]

- When the device is exposed to absolute minimum voltage(-0.3V) of OUTx, what is the failure mode?

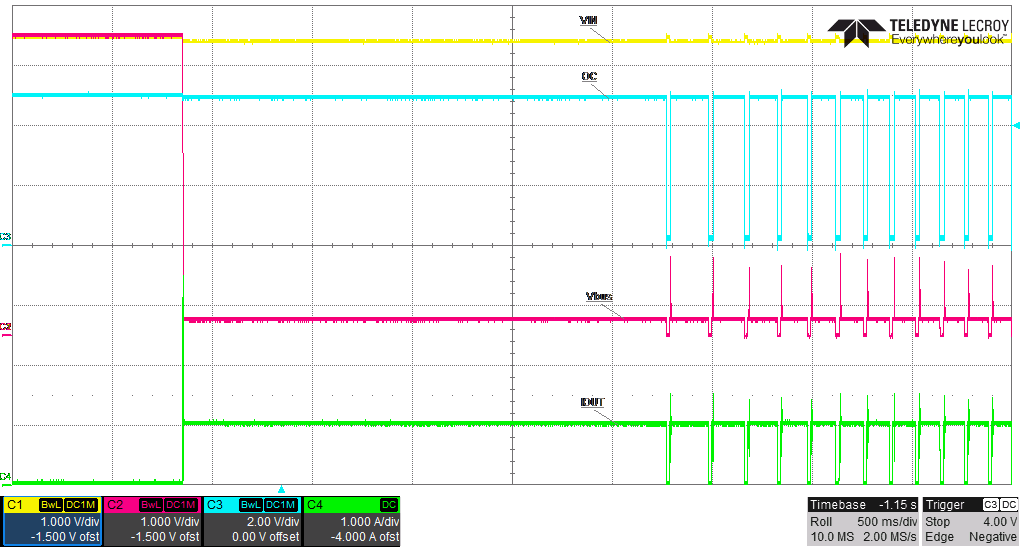

They found failed sample during evaluation. That is short between VOUT1 and /OC1. They were analyzed their board and they found that the cause of failure might be undershoot of OUT1.

So they want to know failure mode by exposed to absolute minimum voltage(-0.3V) of OUTx.

And they want to confirm their guess is right or not.

Best Regards,

tateo