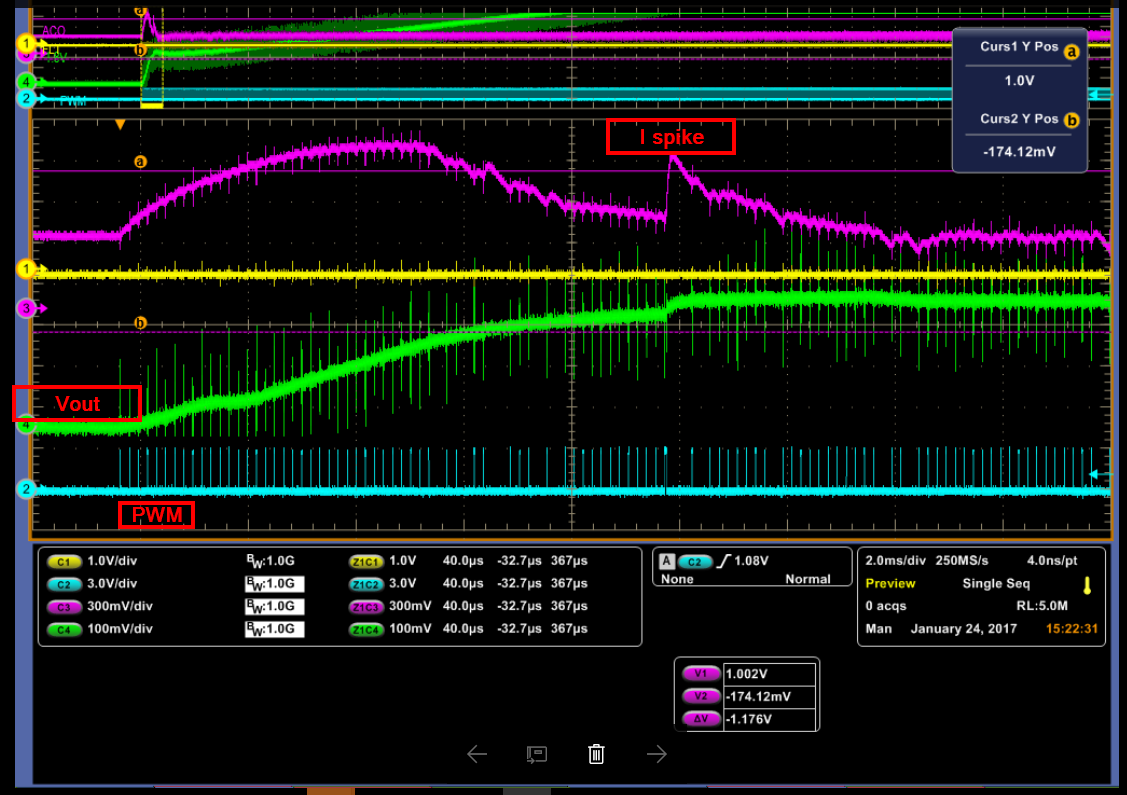

The scope picture shows a current spike (I spike) that happens after the kickstart period as the control system has just started doing closed loop control after the fixed PWM period. The current spike is a direct result of the long PWM pulse.

This current spike does not cross the threshold, but similar current spikes often do and I don't want to rely on retries to patch the issue. The startup control system has adequate phase and gain margins.