Hi,

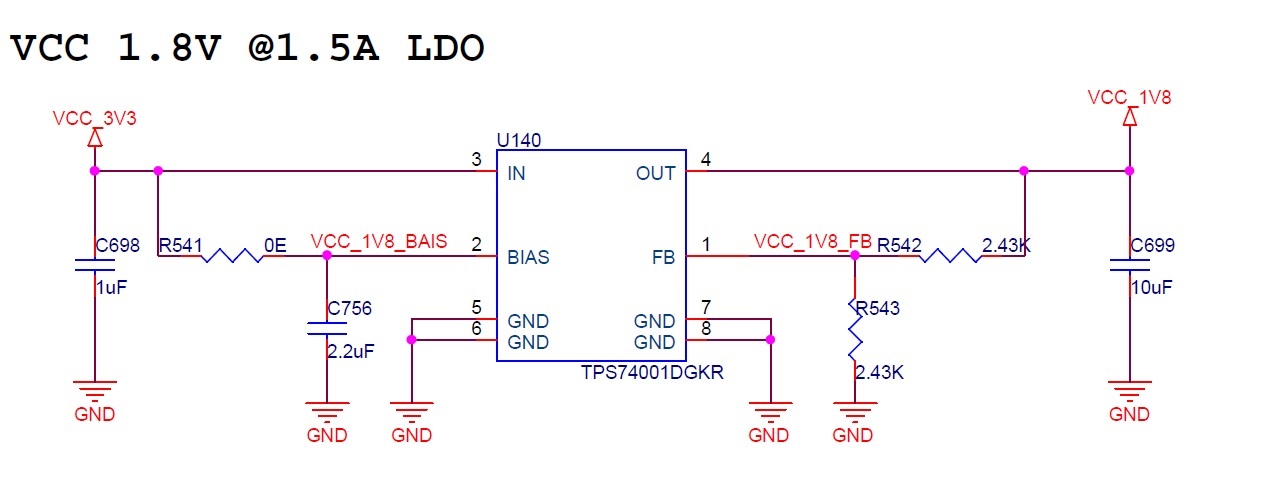

I'm using TPS74001DGKR in my board and I have designed it for 1.8V output.

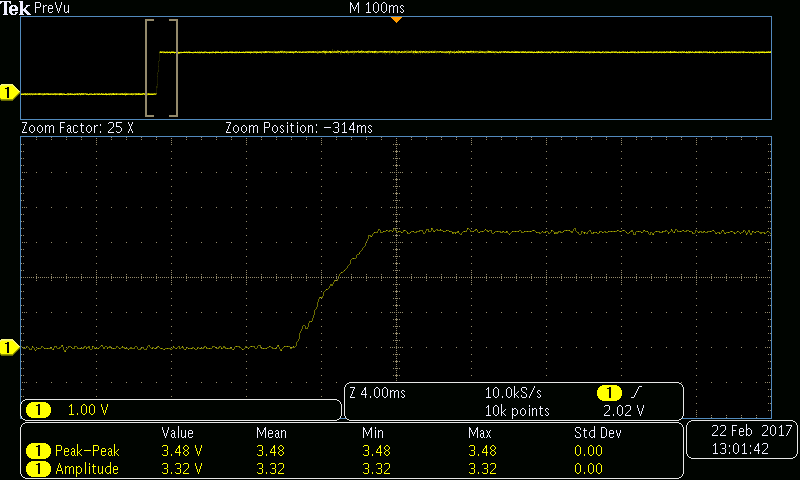

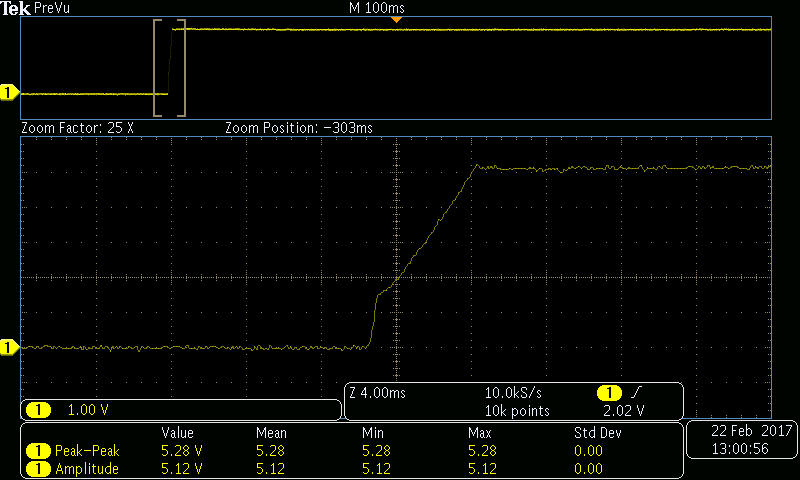

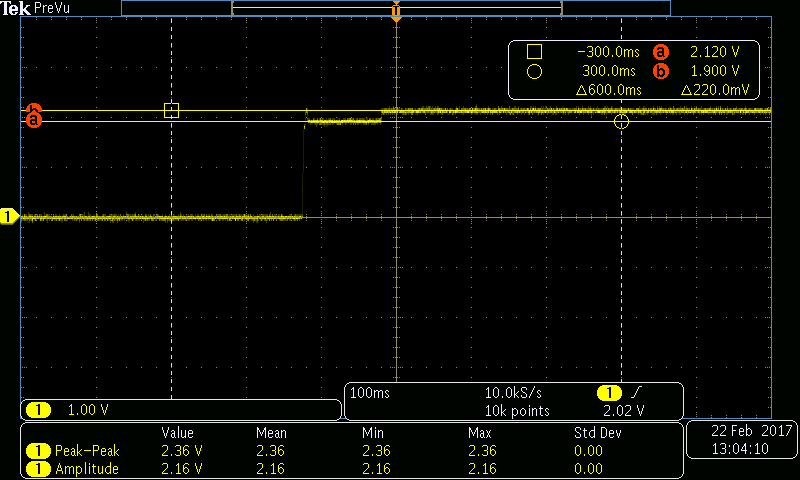

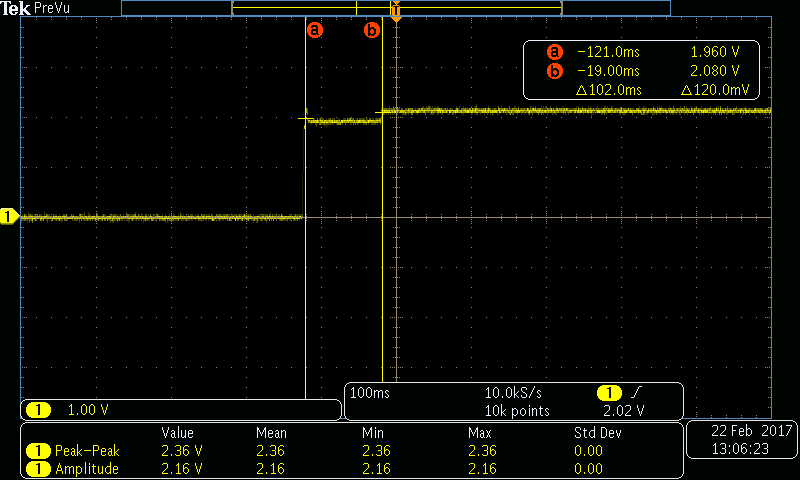

I'm finding that the output voltage is more than specified voltage. (2.02V)

The part circuit schematics is as shown below.

If anyone knows the reason for this behavior of the IC, please let me know ASAP.

Thanks & Regards,

Nanjunda M