Hi,

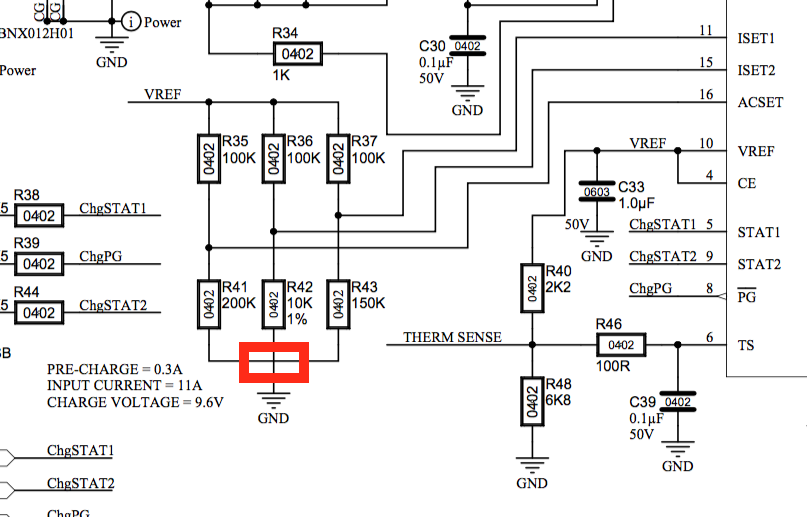

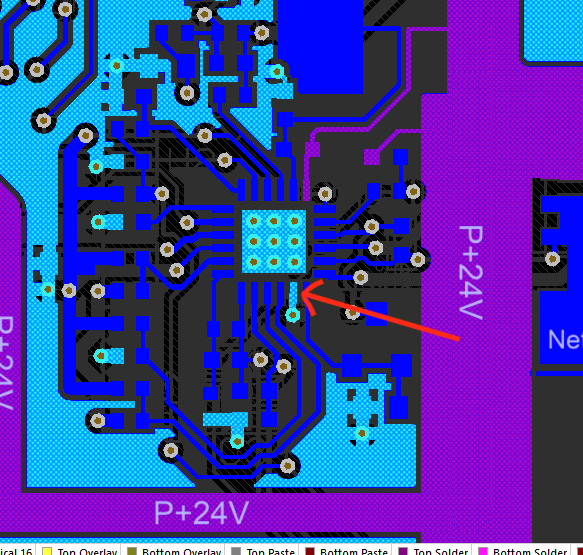

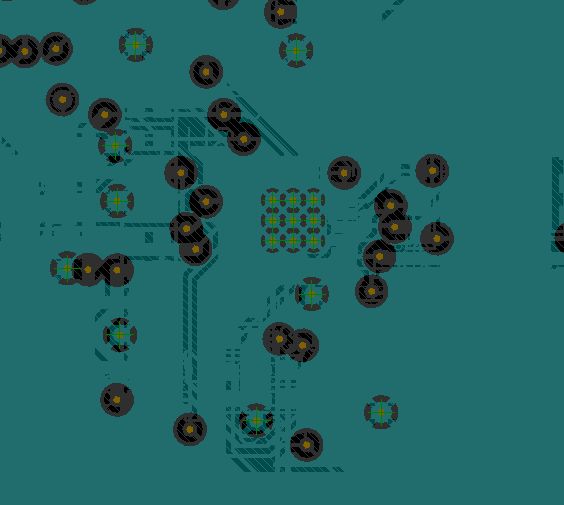

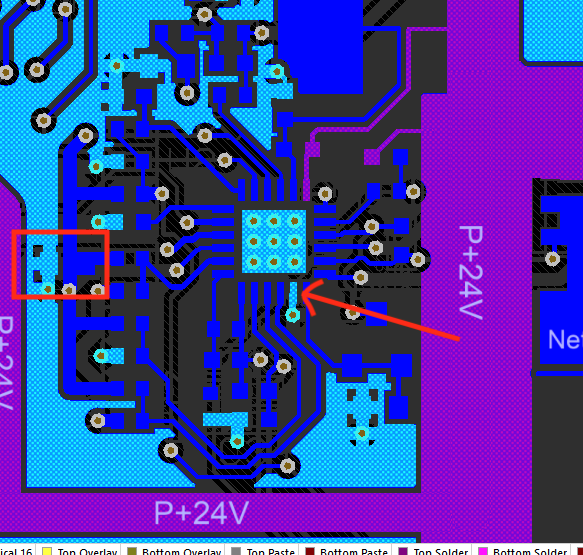

I have a design mostly based on the reference design for a 3S LiFePO4 battery.

I apply 24V to the BQ (checked it on ACN/ACP and on VCC. Draws about 30mA on complete board, so not major fault but the charging does not function.

On closer inspection I measure that Vref is 4.076V instead of the 3V3 specified in the datasheet.

Any ideas why this would be the case?

Other measurements to be done to help resolve?

Schematic below/attached.

Thanks in advance

Ivor