Hello,

I am using UCC28780EVM-021. When I connect it to power supply and start increasing the voltage from 0VAC, I am observing 3 different kind of PWM pulses upto Brown-IN voltage i.e. apprx. 75VAC.

1. 0VAC to 45VAC

2. 45VAC to 75VAC

3. above 75VAC

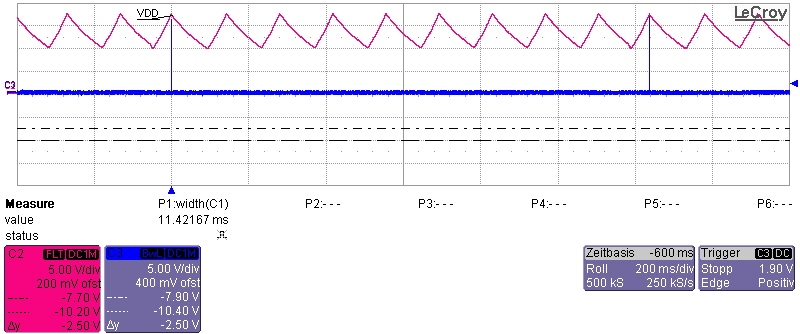

1. In the first range, I have the following waveform. When VDD equals VDDon, there is only one QL gate pulse (Blue in the waveform) of 2us duration (I have checked it by changing the time scale as well). The next pulse comes after apprx. 1.22sec. and this repeats upto 45VAC.

I want to know, which kind of fault is the chip sensing or what is the reason behind this kind of QL gate pulses in the range 0-45VAC? because I have made one circuit and in which the behaviour is not the same. In my circuit there are four QL gate pulses from the beginning up-to 30VAC. and then number pulse reduces to only one pulse.

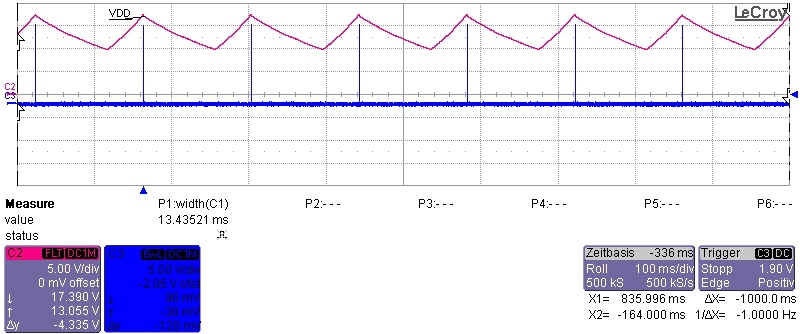

2. When Vin is greater than 45VAC and less than Brown-IN, the waveforms are as follows.

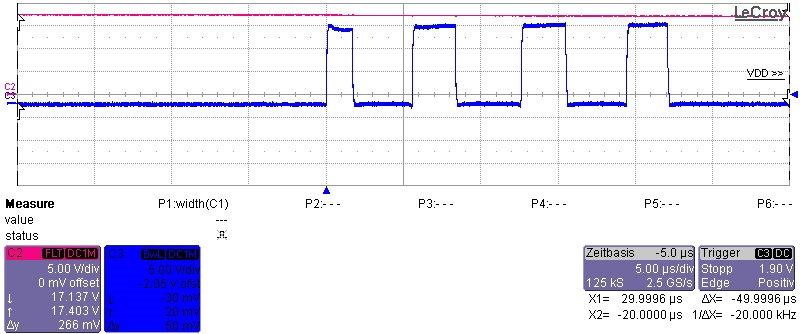

At every VDDon, there are 4 PWML pulses. I think this is the case when it is sensing that Brown-IN voltage is not reached. Because it behaves the same till Brown-IN voltage. And above the Brown-IN voltage, it works normal and we have constant VDD and QL gate pulses depending on load.