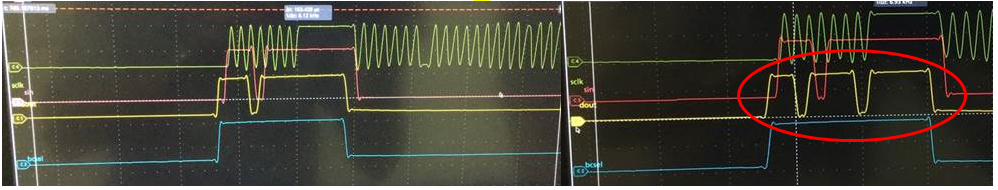

1. The output data of TLC5943 Sout confirmed that TLC5943 had data misinterpretation problem. The writing value of BC: EF will be misinterpreted as DE.

EF: 1110 1111 DE: 1101 1110 (just moved one place to the left)

(confirmation of normal SIN\SCLK data)

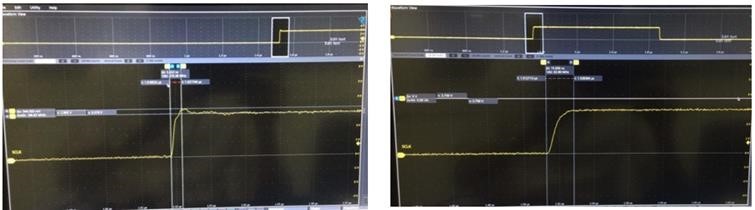

2. It is confirmed that there is a 0.35v overshoot on the current design of SCLK, with a rising edge of 3ns. Experiments show that the parallel connection of a few pF capacitors on SCLK (rising edge can be delayed to about 10ns), which can improve data misinterpretation.

Need TI help confirm:

1. TLC5943 has specific requirements for SCLK rising edge delay, and does the rising edge of 3ns meet IC design requirements?

2. Can parallel capacitors delay the rising edge on SCLK fundamentally solve the problem of misinterpretation of the data?

3. During the test, it was found that if the BCSEL operates at normal times when SCLK is high, there will be a risk in the time sequence?

Thanks