Other Parts Discussed in Thread: BQSTUDIO

Dear Sir,

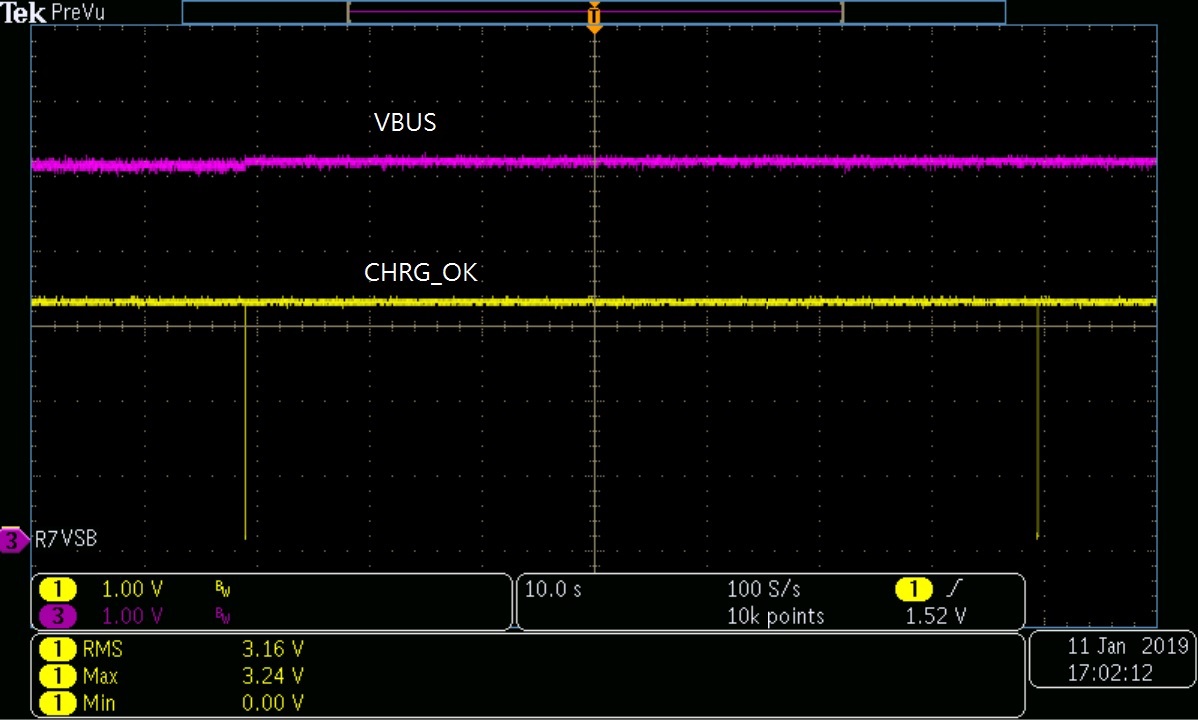

My customer have issue, CHRG_OK will drop.

I check below 3 condition didn't have happen:

• VBUS is above VVBUS_CONVEN

• VBUS is below VACOV

• No MOSFET/inductor fault

Could you advise what kind condition will make CHRG_OK drop?

Thanks!

Steven