Other Parts Discussed in Thread: LM5141-Q1

Hi,

My customer will use LM5141-Q1.

My customers will buy TI's EVM and plan to do a test before designing.

The specifications are below.

Please tell me the changes in EVM to meet the following specifications.

(specification)

VIN : 16V(min), 24V or 48V(typ), 60V(max)

VOUT : 12V

IOUT : 0.1A(typ), 3A(max)

Operating frequency : 2MHz

Operating mode : FPWM

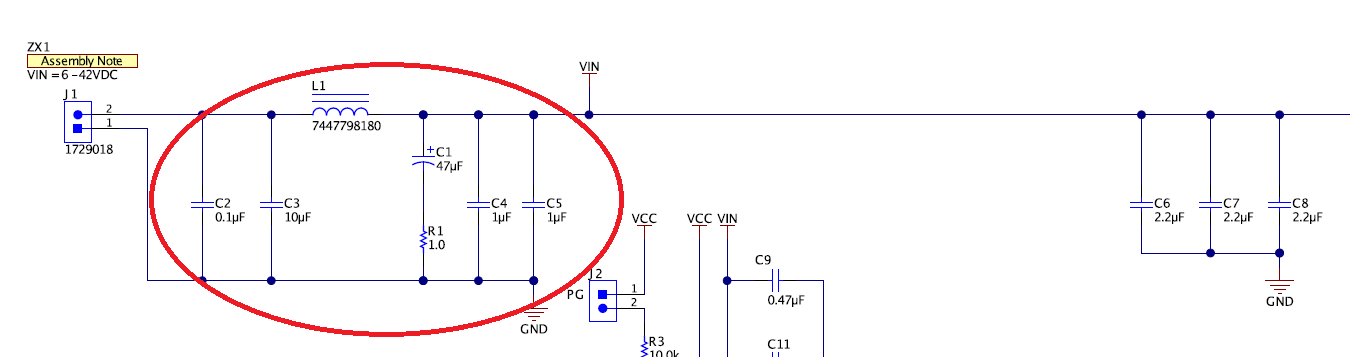

Also, the input filter is not used because the substrate size is small.

Also, I want to reduce the output capacitor as much as possible. Therefore, please tell me the minimum required capacity value.