Tool/software: Code Composer Studio

In DPWM Resonant Mode, How to Limit maximum operating frequency and adjust the DPWM for 50% Duty?

How to Configure the register parameters?I refer to TI LLC HB code,to Configure the DPWM and Filter register。Now I can adjust the frequency by EPA0 input, But i can't Limit maximum operating frequency (Can Limit Minimum frequency ).And I don't konw how to adjust the duty for 50%.

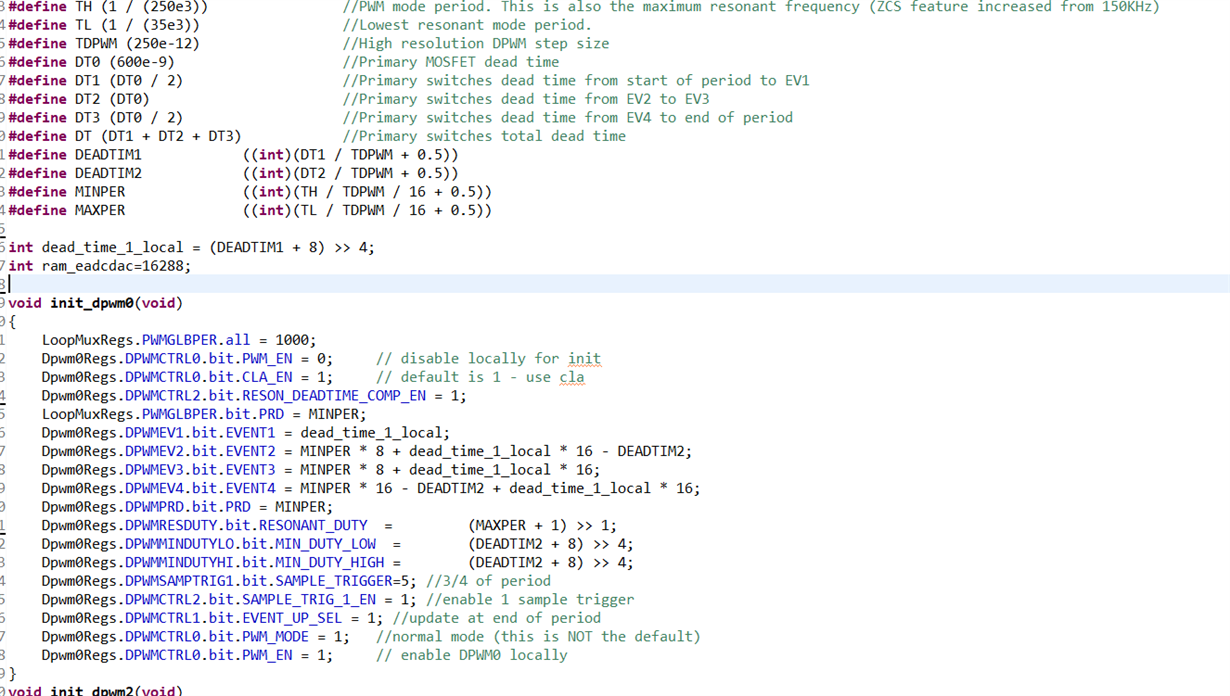

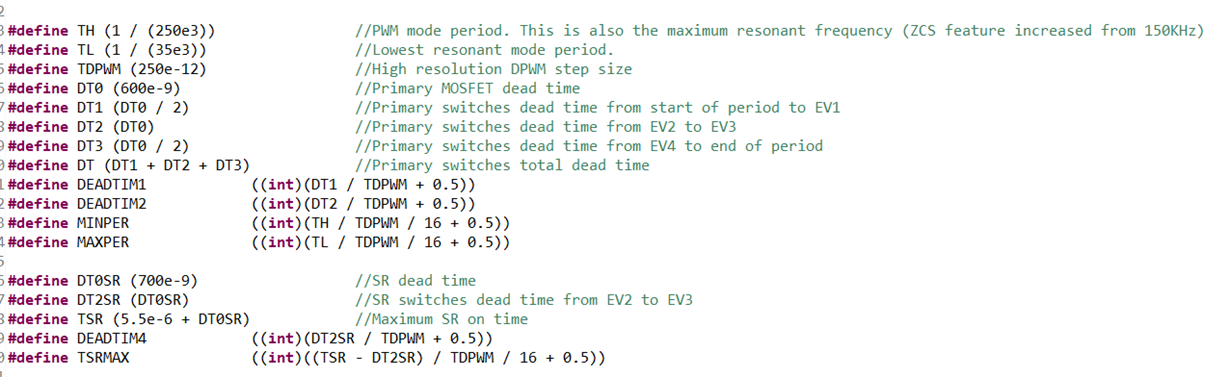

Here are some of my code(If have any suggestion or have any mistaken please tell me):