Hi, Jaden

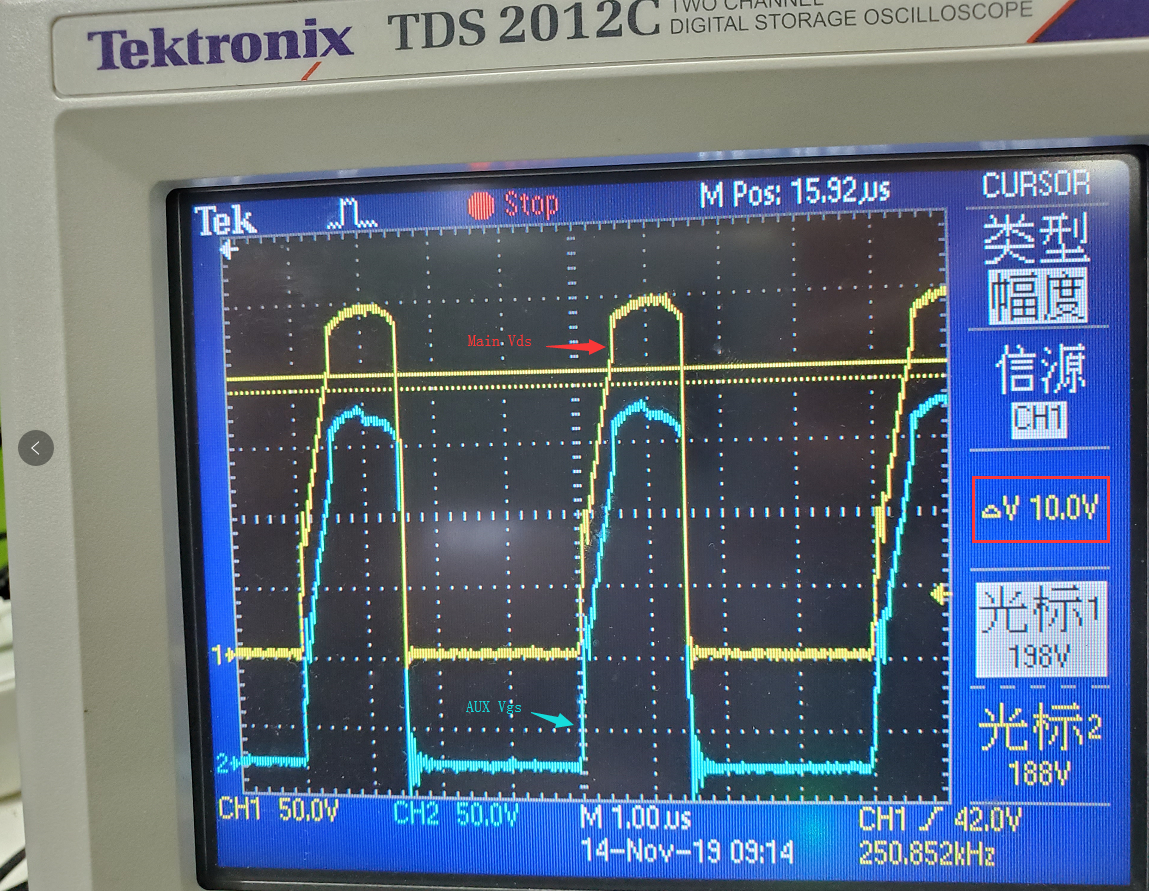

Please look at my waveform and see if ZVS has been implemented. And I feel the rising edge of the main switch Vds is a little strange, do not know what is the reason, according to the principle should be vertical up.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi, Jaden

Please look at my waveform and see if ZVS has been implemented. And I feel the rising edge of the main switch Vds is a little strange, do not know what is the reason, according to the principle should be vertical up.

Hi Tracy:

I will assign Jaden to answer you. thanks.

Hi Tracy,

Could you please tell us what is the test condition when you captured the waveforms , such as , the input voltage/output voltage/ output load.

And please attach your schematic as well. in your second waveform. I guess AUX Vgs was measured on controller side , could you please captured it on MOSFET side ?

Thanks.

Hi Jaden,

Thank you very much for answering my question

The following figure is the waveform of MOS tube.The test conditions is that the input voltage is 77V and the output is 48V@1A. I wonder if I have a bad control of dead zone time, but I have tried many values, but the effect is not obvious, and ZVS is not implemented

Another phenomenon is that when my voltage rises to about 110V, the Vds waveform will become very messy. May I ask why this is caused?.

Hi Tracy,

With limit information, I can only guess what happened on your board. Could you please try to decrease the magnetizing inductance of your transformer.

In this way you can get a higher peak magnetizing current when main FET turn off . higher magnetizing current will cause a sharp DV/DT of main FET Vds.

Also it's benefit for the implementation of ZVS turn on main FET . since you can get a large negative current during AUX FET turn on.

Thanks.

Hi Jaden

I followed your advice and adjusted the magnetizing inductance of the transformer to half of the previous value and changed it to 172.5uH. The result is as follows:

1. Waveform has been greatly improved, and ZVS can be realized at low load. The higher the load is, the highest; the worst result is that Vgs rises when Vds is about 60V;

2. After several minutes of operation, the transformer becomes very hot and the load output is intermittent;

3, improve the input voltage, Vds waveform will be left and right jitter.

Please refer to the attached schematic diagram.Thank youUCC2897A SCH.pdf

Hi Tracy,

We have a application note which can guide you how to design a ACF board with UCC2897A, I attached it for your reference.

Also we have EVM board on line. you can order one to test it . The link as below:

0044.Understanding and Designing an Active Clamp Current.pdf

Hi Jaden,

I have both the two EVM and this document you mentioned and have analyzed them.But for the problems I'm having right now, neither of them will solve it.

Hi Tracy,

There are too many questions in this post. we have to close this post. could you please create a new post with your new question.

Please attach your waveforms and detailed descriptions , We can't identify what's happens on your board without sufficient information.

Thanks.