Other Parts Discussed in Thread: ISO5451, TMS320F280049, ISO5851

I have the following:

- 4 switch 3-phase interleaved bi-directional buck boost converter (please refer to TMS320F280049: CMPSS query to implement peak current mode control of a 4 switch 3-phase interleaved bi-directional buck boost converter post for a diagram of my setup)

- 2 boards in total: Controller Board and Power Board

- 12 gate signals

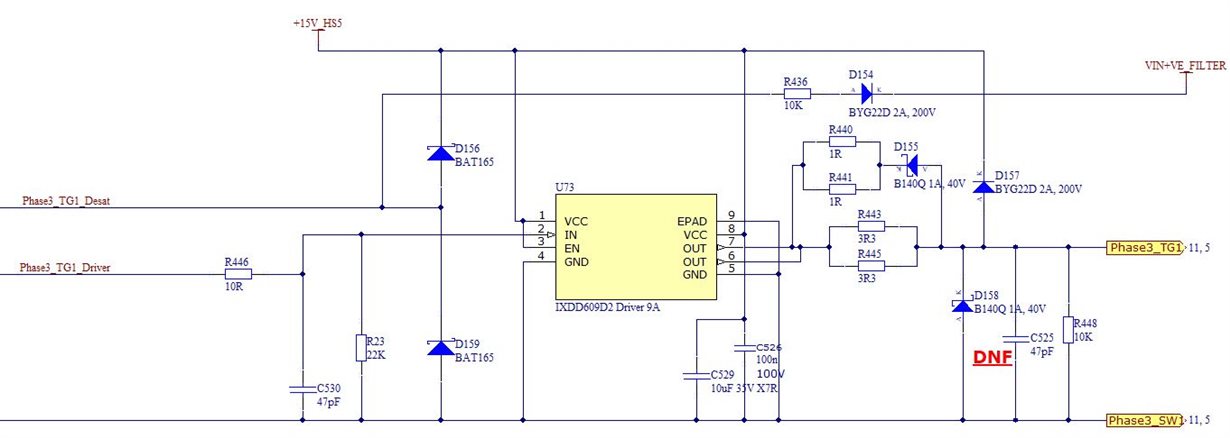

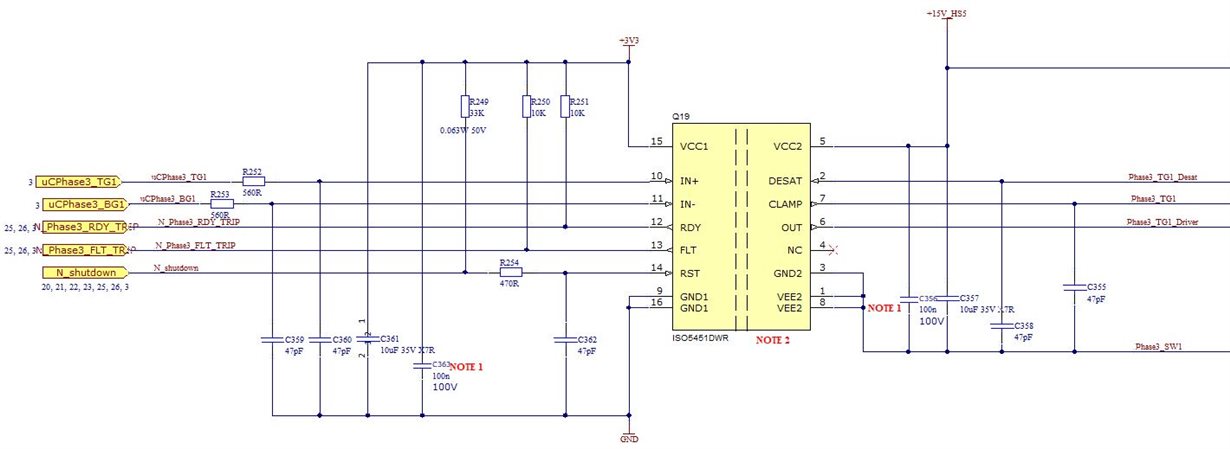

- 12 ISO5451 gate drivers are on the Controller Board

- 12 IXYS IXDD609 buffers on the Power Board

- All 12 gate driver circuits are schematically identical

- The gate signal connections are connected via non-ideal long track traces from the Controller Board to the Power Board

- The switching frequency is 70kHz

- All gate signals to the ISO5451 are generated using the PWM module of the TMS320F280049

- The TMS320F280049 is operating at a 100MHz clock frequency

- The tests were done with no inductor present and no supply voltage across the bridge

- Desat protection and miller clamp is part of the circuit and permanently enabled

- 22nF gate capacitance of each MOSFET

- 0 to 15V gate signals

Out of the 12 gate drivers, I have a problem with one displaying the following characteristics causing a shoot-through.

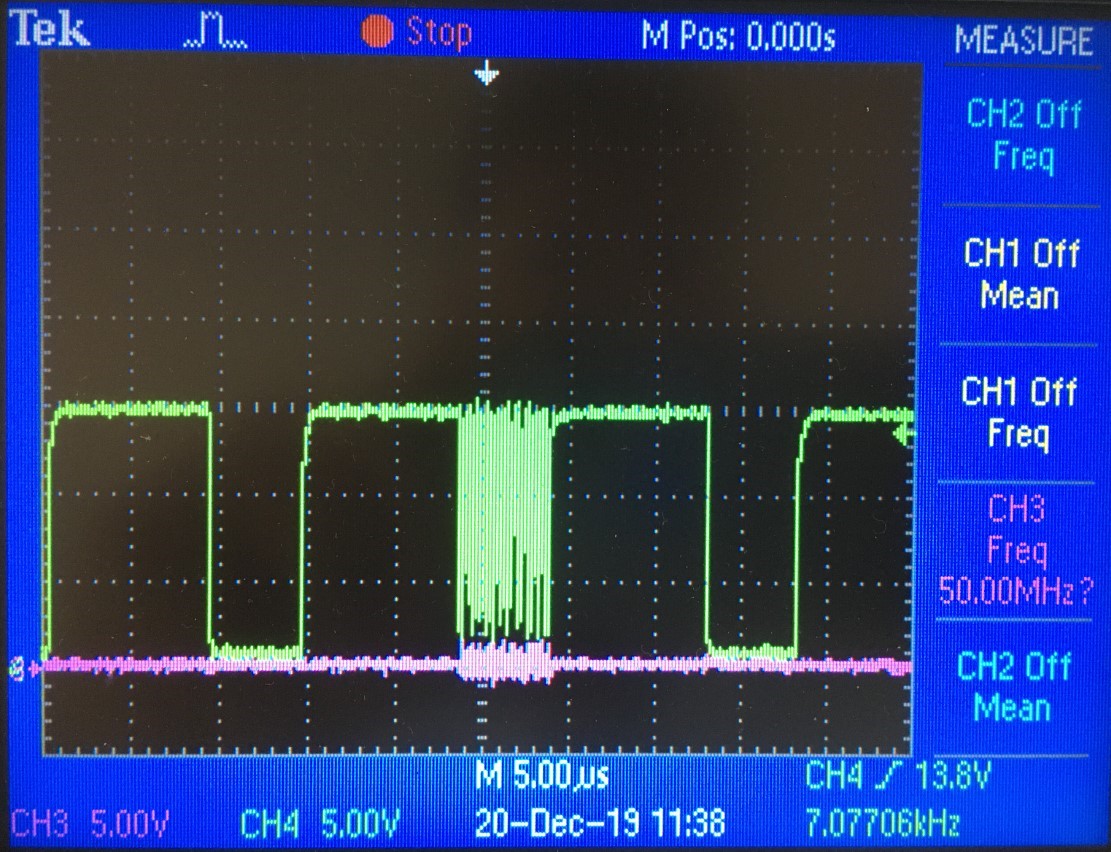

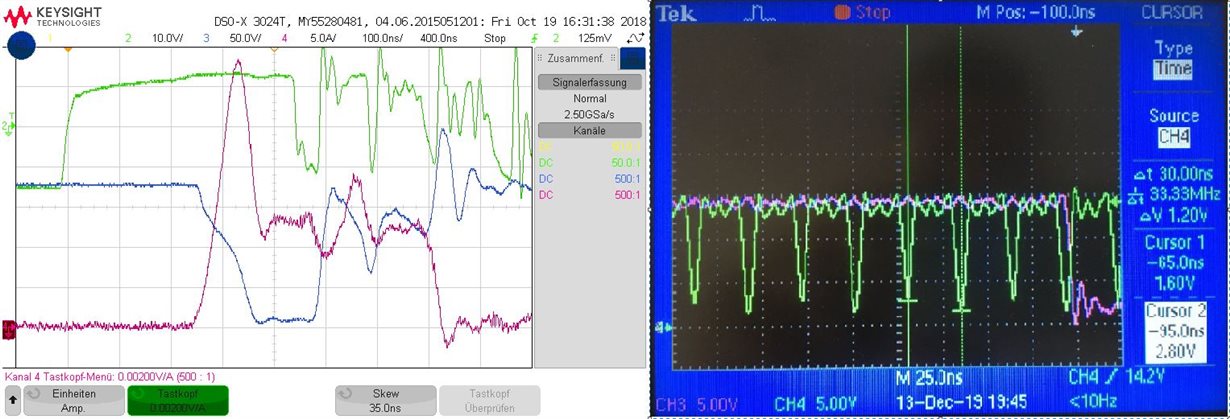

Green is the top gate signal

Pink is the bottom gate signal

I am baffled why I am observing sporadic 33.33MHz oscillations on the top gate when the bottom gate is high. This only occurs on only one of the 12 gate drivers. I have also bypassed the buffer with the same results.