Hi, Technician or Manager,

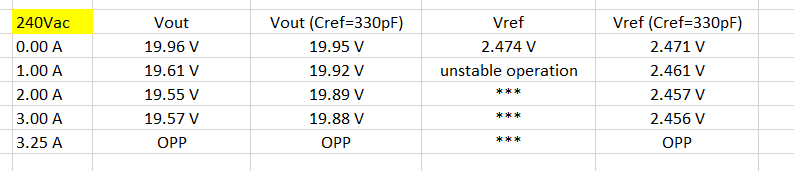

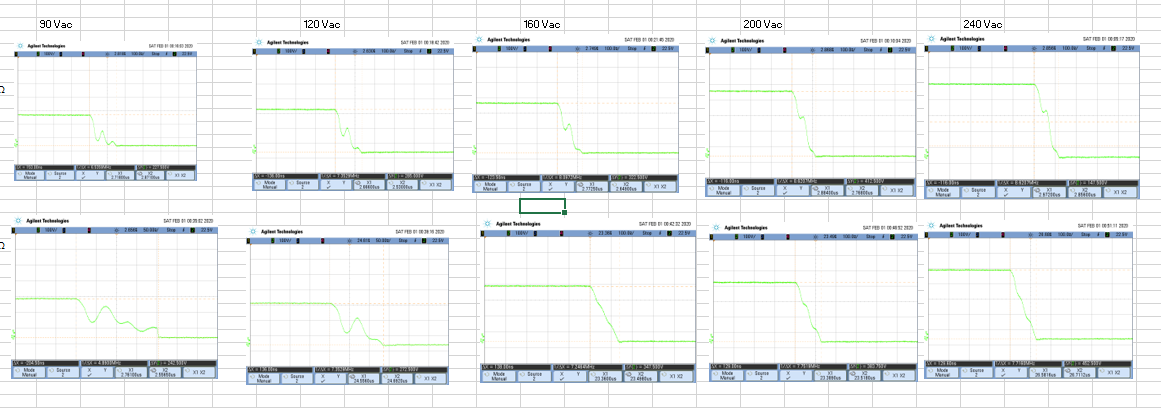

I have designed a 65-W prototype by using UCC28780. I found that at 90Vac input, the Vout only drops 0.07V when the load current increases from 0A to 3.25A.

However, when the line input voltage increases to 220Vac or 240Vac, the Vout drops nearly 0.9V from 0A to full load (3.25A).

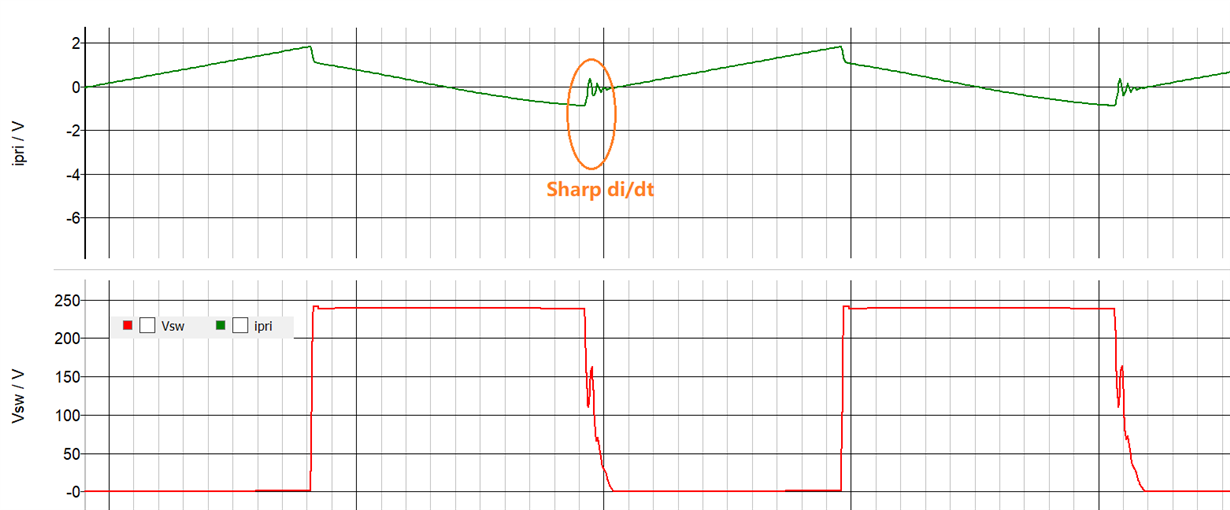

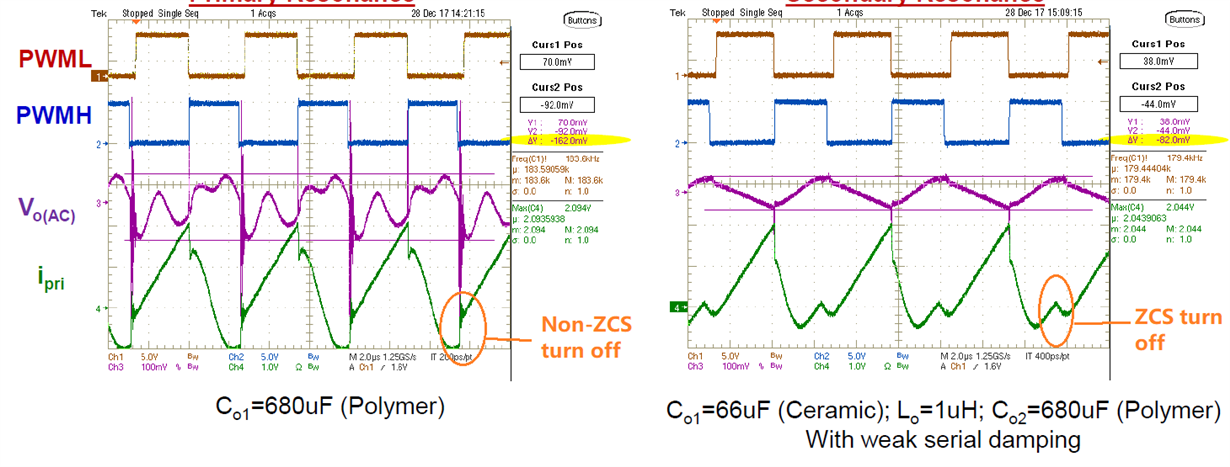

I have tried to decrease the Ropp from 1kOhm to 250 Ohm, it does not work. and I tried to increase the Cout from 680uF to 1360uF, and the Vout also drops a lot at the high line input from 0A to 3.25A.

What might cause such problems? Could you give me some suggestions about how to solve it? Thanks!