Hi,

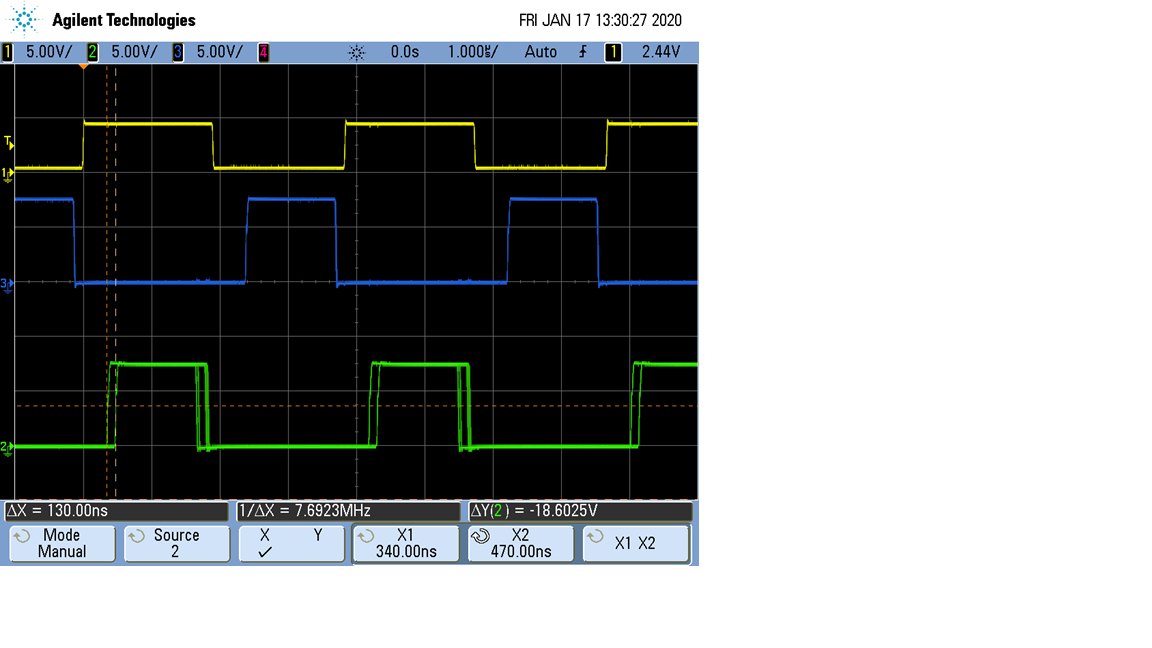

I have a 20-40V to 48V boost, 10A max 260kHz using 2 interleaved LM5122s wired as per Figure 31 in the datatsheet. Over narrow input voltage ranges, the Slave timing will jitter back and forth 130ns. Below this input voltage range it will be stable and follow the left hand timing and above the range the right timing. This range is load depend and, at 8A its around 31-32V and easy to find. At 4A maybe 25V and the span is ~100mV so hard to find.

Although not clear from the the capture below the duty of the lower waveform does not change substantially. So its not sub-harmonic oscillation. It also occurs for duty cycle less than 50%.

The delay from a falling SYNCOUT to Master LO is the same as a rising SYNCOUT to right hand cursor. Hence it appears right hand cursor is the correct Slave timing. So the Slave is starting early 130ns sometimes and not 130ns late.

This appears to be a Slave External Sync issue but I'm perplexed as to what? Note SYNCOUT does not change with input voltage and remains a clean square wave

1: Master SYNCOUT

3: Master LO

2: Slave LO