Other Parts Discussed in Thread: LM5022

Hi,

I'm designing a flyback using the LM5022

VIN: 30V to 600V

VOUT: 15V 2W

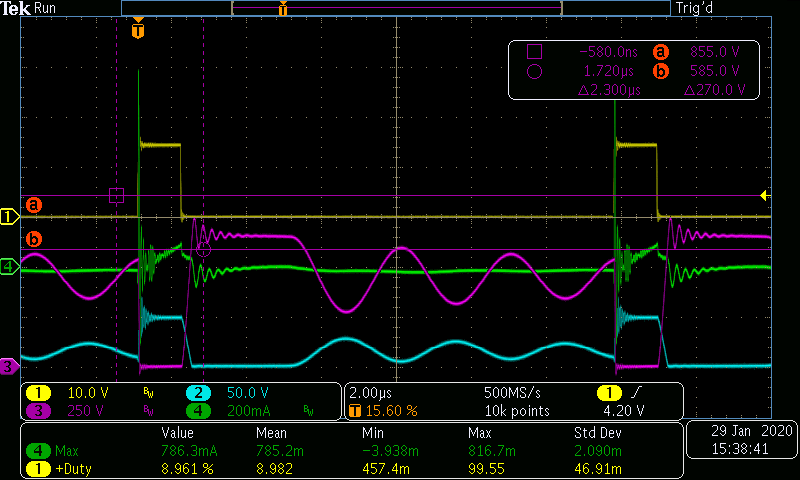

- CH1: VGS Q102 (principal sw)

- CH2: VAK D4 (output diode)

- CH3: VDS Q102

- CH4: iDS Q102

2 questions:

- VIN=400V, LOAD=103R0. the inrush current at the turn ON of the MOS is principaly due to transformer capacitance ? So to limit the peak current, a "new" winding is recommended... any suggestion ?

- I'm not able to have a stable PWM at low voltage (i.e. 60V), is there a "clean" way to select components to avoid this ? I think it's start with a good slope compensation.