Other Parts Discussed in Thread: TMS320C6742, , TMS320C6746, TMS320C6748

Tool/software: Code Composer Studio

Hi

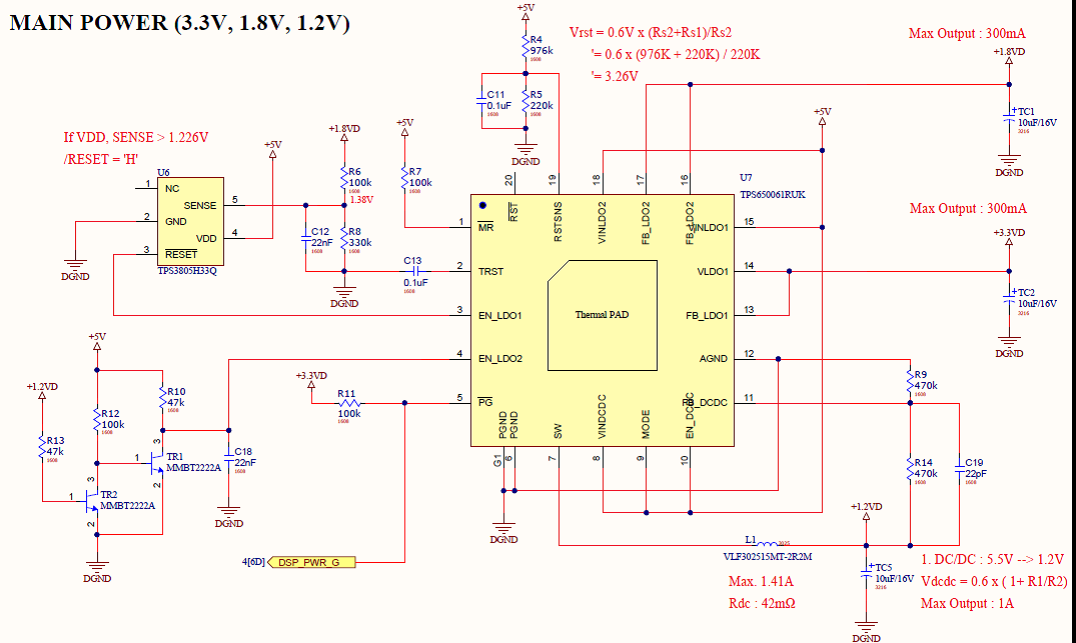

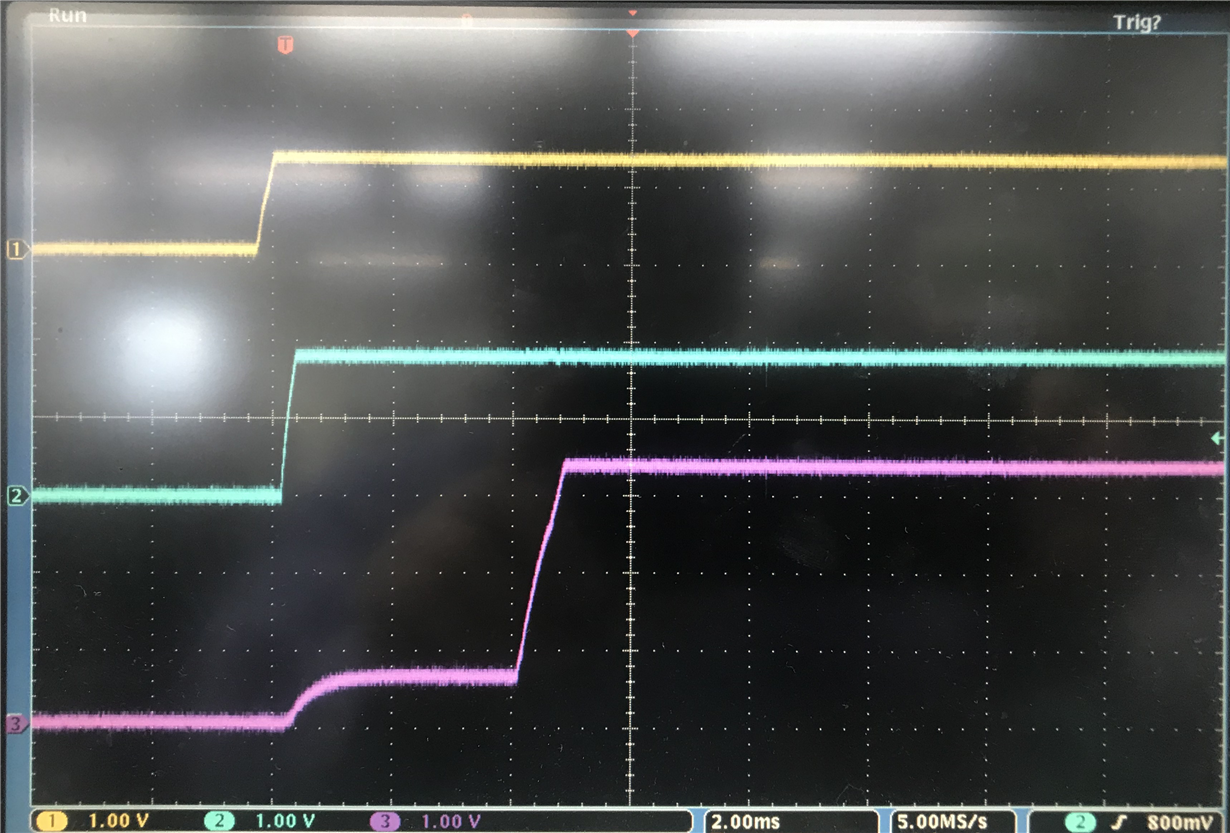

The circuit was designed as shown in Figure 1 with reference to “SLVA490–October 2011, Powering the TMS320C6742, TMS320C6746, and TMS320C6748 With the TPS650061”, but the turn on time of 3.3V is 3.7ms + 900us (Figure 2). I understand that the 3.7ms delay is due to the TPS3805's sense resistors (R6, R8) and capacitor (C12), but I don't understand what the 900us Ramp Time is. SLVS810C's VLDOx Ramp Time is typical 200us and there is no Min / Max value. Do you know how much Min / Max is? And can you see why about 900us Ramp Time occurs?

Figure 1, TPS650061 Circuit

Figure 2. TPS650061 Power-On, Ch1 : 1.2V, Ch2 : 1.8V, Ch3 : 3.3V

Regards

Oh