Hi TI Team,

We are using TPS40305 switcher with 5V input and 3.3V, 9A output. We are facing issue in pre-compliance test (FCC Part 15B). We are getting out of limit 160MHz broadband noise. Can you please help on reducing this broadband noise?

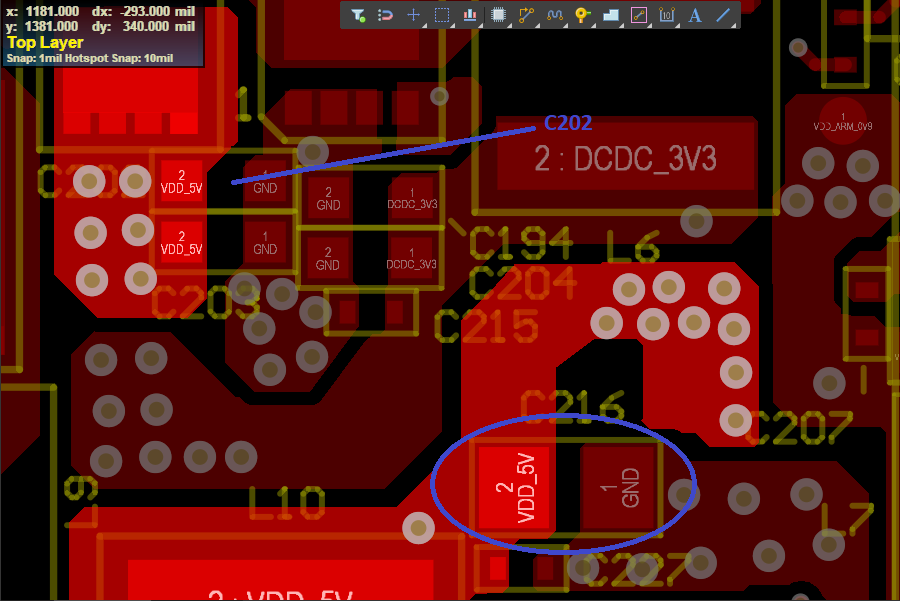

Attached is the snapshot of schematic and placement & routing.