Hi,

When the input signal of LMG1020 is 5V but the output is between 0.1V and 1.5v,and i resolder a few pieces of LMG1020 to test the result remains the same,so what do you think might be the cause?

Please look at the schematic。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

When the input signal of LMG1020 is 5V but the output is between 0.1V and 1.5v,and i resolder a few pieces of LMG1020 to test the result remains the same,so what do you think might be the cause?

Please look at the schematic。

Suy,

Thanks for your question:

Can you provide plots of gate, VDD, inputs

And you are not using any Resistor on OUTH/OULTL?

best

DImitri

Hi Suy,

The output is measured between 0.1V and 1.5v, and it seems it has certain misconnectioning if the 5V is solidly applied to the part. If the part is soldered with all connection right on, the output should be high or low, it shouldn't be a unstable voltage measuring between 0.1V and 1.5v. Do you have an X-ray to tell the connection is solid, or how can you guarantee the connection from soldering. Thanks.

Wei

Thanks Wei, Dimitri,

HI Suy,

Thanks for reaching out about lmg1020.

Are you using the lmg1020 EVM or your own pcb?

Is the land pattern that you used from the datasheet dimensions?

How are you soldering the 1020?

Can you take a scope shot to show the output (OUTH to GND) is 1.5V during switching?

Thanks,

Hi Jeffrey ,

The board is our own PCB.And i have pointed the problem that the value of C21 can affect the output of LMG1020,when using the 8pF the Vgs is low then change to 27pF the Vgs gose high,and the luminous power of LD5 increased a lot.

Thus i have another question,i want to use LMG1020 to output a 2ns pulse,the value of the R12&C21 is correct?

Hi Suy,

Thanks for the update.

I tried to find r12 and c21 but I cant seem to find it on the schematic you provided.

Can you send a snippet of your actual schematic to see r12 and c21?

Also can you send a snip of your layout that includes the whole gate loop?

Thanks,

Thanks for the update,

1020 needs its VDD cap close to the VDD and GND pins.

I see c29 is a feed through cap for low inductance gate loop and high peak source current, however there also should be a 1uF XR7 cap on VDD for stability.

Its possible the VDD cap placement is not optimal in layout. Which is why I asked to review layout portion.

To confirm what the issue is, Can you take a scope shot of the issue with waveforms?

Also highlight on the schematic where the probe points are.

How are you pulsing IN+ and IN-?

Thanks,

Thanks for the update Suy,

Why choose to pulse both IN+ and IN- delayed by 2ns rather than a 2ns pulse on IN+?

In order for VDD to stay at 5V 1020's VDD pin needs two caps. A high frequency feed through cap for source current, which I see on the first schematic and a lower frequency 1uF for stability, which I don't see on VDD.

Can you confirm VDD pin has these capactiances?

Can you confirm the 1020 supply is at 5v and 1020 VDD pin is at 5v?

What is the V/div on this waveform? Is the pulse a 4V peak?

The pulse looks good if the peak were higher. it may be that the VDD pin is not seeing the right voltage due to the above capacitance values or even cap layout placement of the VDD cap, which is why it is possible the layout may have caused this low VDD issue.

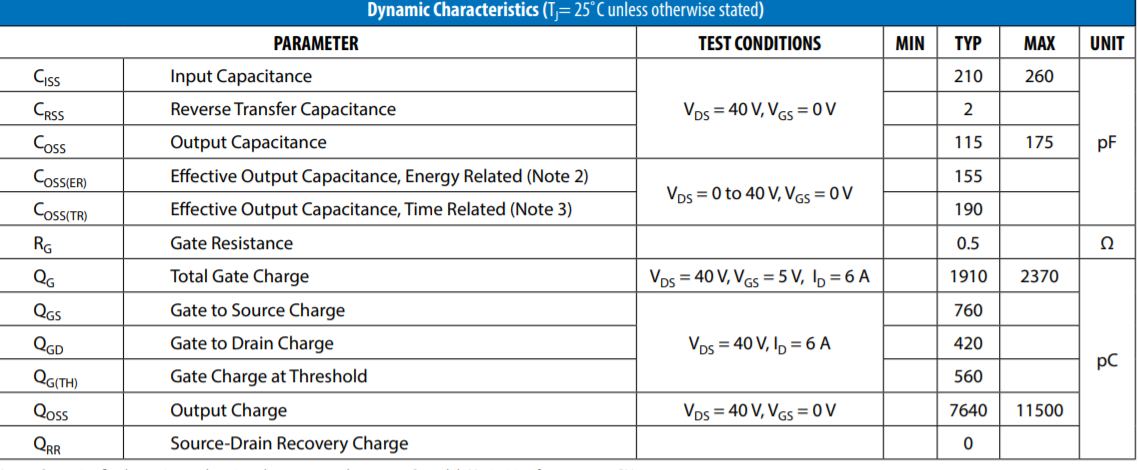

Also the rise/fall times are about 3x as slow, are you using a gate resistor or large gate charge fet?

Does the issue still happen with no fet/load populated?

Thanks,

Hi Jeffrey,

Not both IN+ and IN- are delay 2ns but only the IN- delay from IN+ .

You are right that i used only 0.1uF feed through cap,i‘m sure that the 1020 supply is 5VDC

The waveform is the output of 1020,but the 4V peak is unormal ,it might be output 5V peak

The output of 1020 still when without FET,and the gate resistor and charge are very small

Thanks for the update Suy,

Looks to me like 1020 is switching ok then.

Can you show me a waveform of the issue you are describing?

Thanks,

Suy,

Jeff should get back to you early next week on your latest question.

Thanks for your patience.

Regards,

-Mamadou

Hi Suy,

The 1020 can achieve a 1ns pulse width typically however it's possible to achieve 800ps pulses if optimal layout and signaling is there.

Thanks,