Hi Support team

According to the datasheet, when MOSFET is ON, INN PIN will be -100mV, nFGD will be high

When MOSFET is OFF, INN PIN will be -600mV, nFGD will be LOW

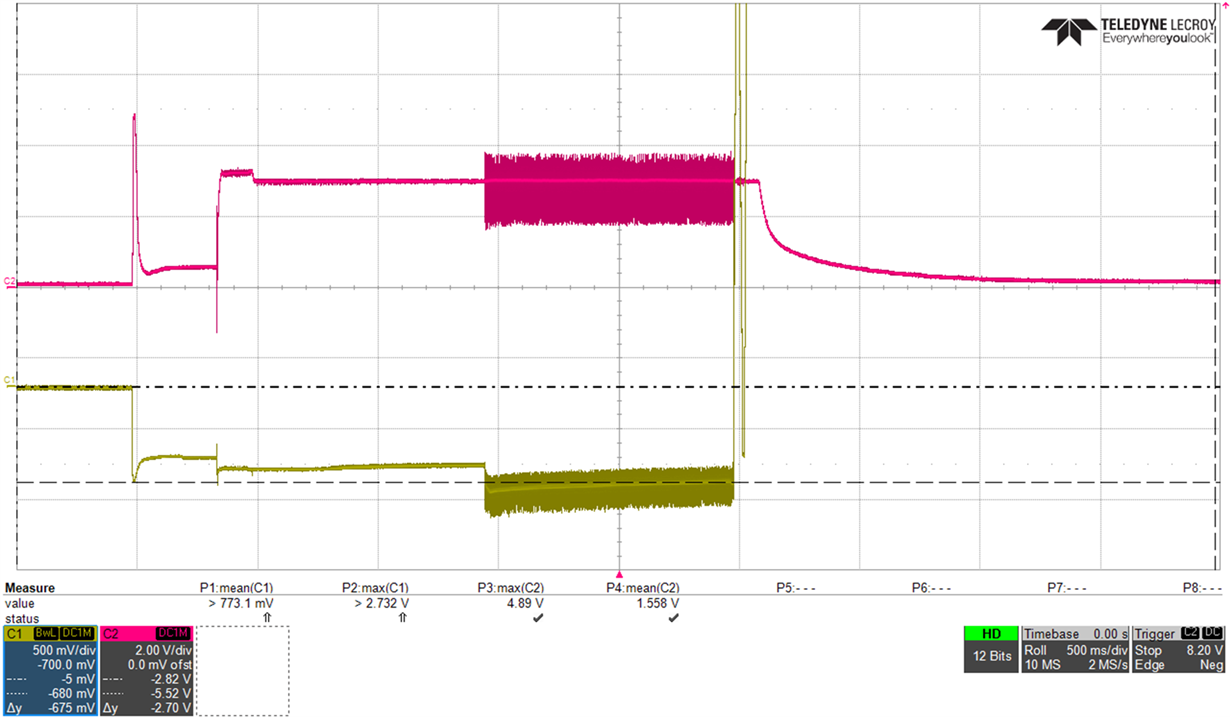

But the signal I measured at CH1 is -700mV, CH2 is also high, CH2 should pull LOW but not LOW.

may i have your comments?

CH1:PIN6 CH2:PIN4