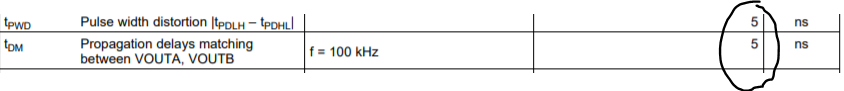

We are considering your UCC21520-Q1 drivers for our future designs and I have a question about the minimum dead-time that can be reproduced correctly by the driver. What is the minimum dead time that could be used, but still to avoid overlapping between the signals at the driver's output (due to some mismatch of the propagation delay times)? We do not use Rdt to set the dead time, it is done by the control unit externally (for both INA, INB).

Thank you very much in advance!