Other Parts Discussed in Thread: TPS54824, TPS54A24

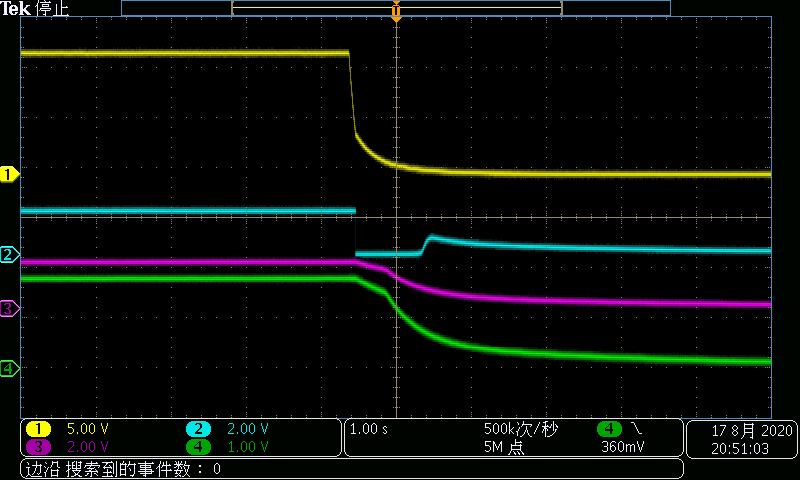

During the EVM test, it was found that when PGOOD outputs no load during the power-down process, a voltage of 1v will be generated after 1 second. The output voltage is very low when the output is loaded. Where does this voltage come from?

The blue one is PGOOD. Pink is PGOOD PULL UP