Other Parts Discussed in Thread: ALLIGATOR

Hello,

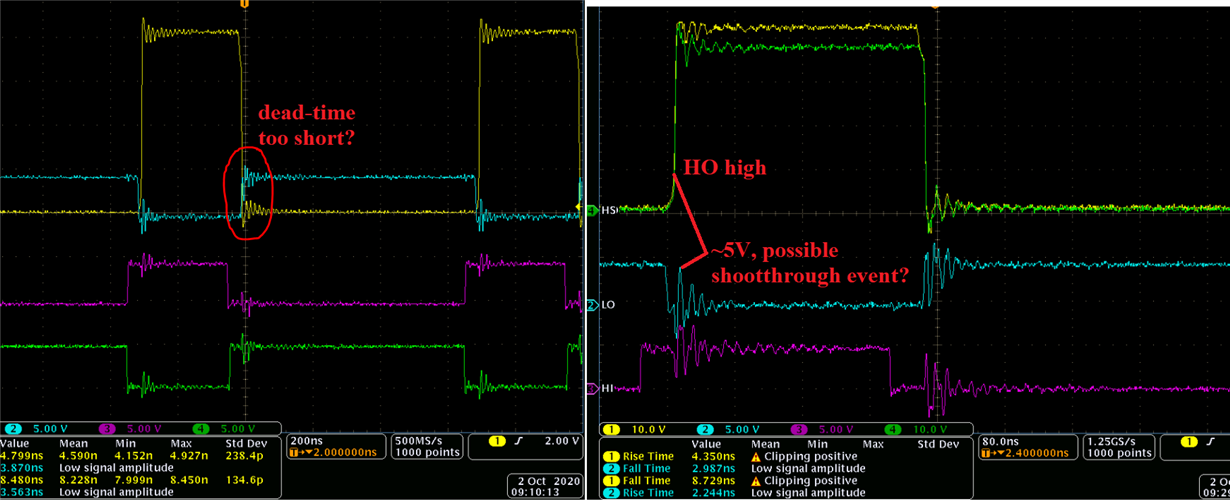

MOSFET blow up during load testing, I have below questions:

1- Vpp was between -2.5 and +2.5, that could be an issue to blow up Mosfets? PS: Mosfet was working for testing current from 1 to 10 ampere then suddenly blow up and it happened for 2 kit boards.

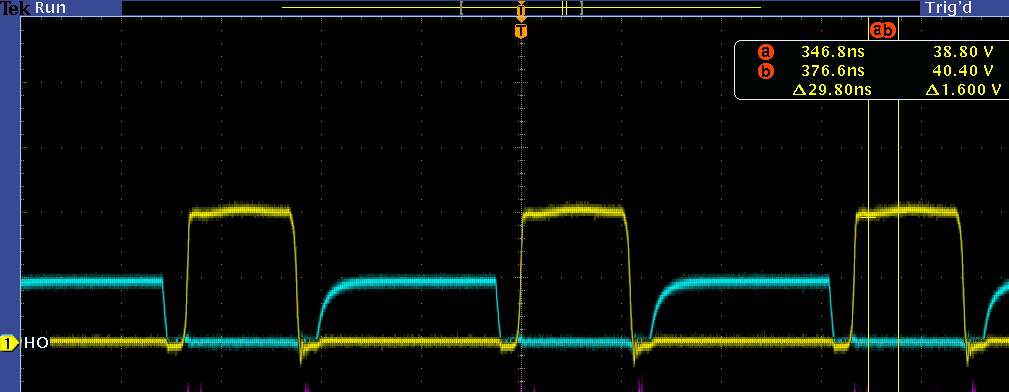

2- I use DC power supply (Agilent N5747A) during the test i read Vin=40.01V, Iin=0.4A (the current that shows on power supply), duty cycle=40%, Vout=15.82V and Iout=1A. I used DC load. so in this case Pout=Vout*Iout is bigger than Pin=Vin*I in??? how it happened? i know efficiency should be around 90-95% depends on load current.

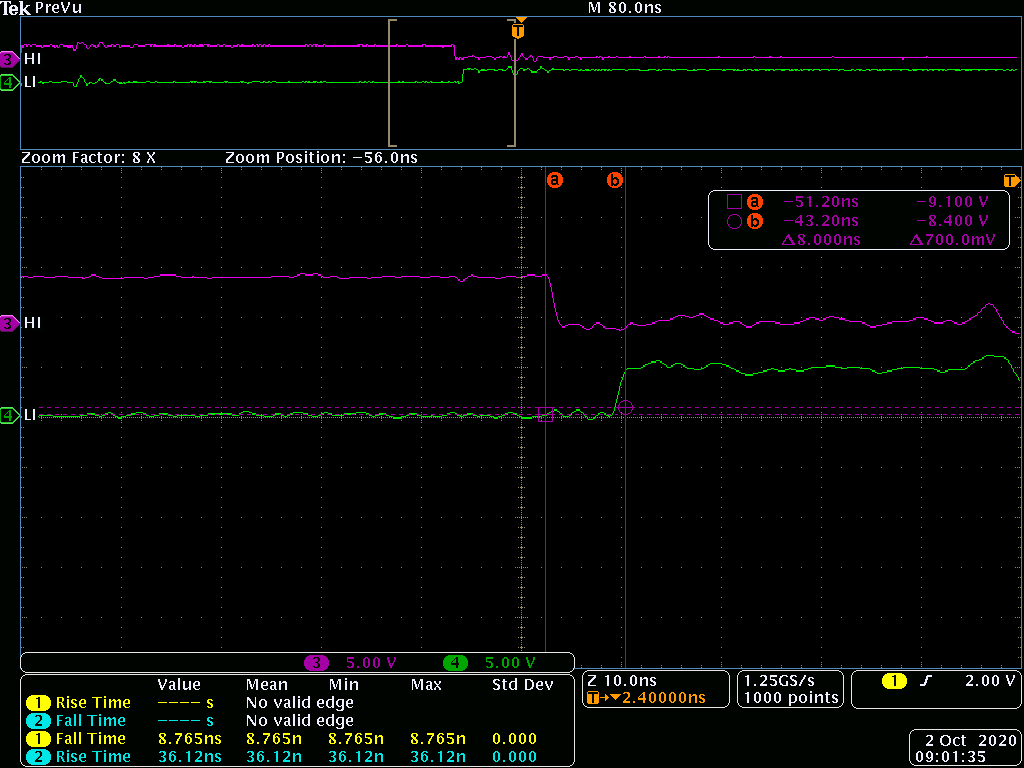

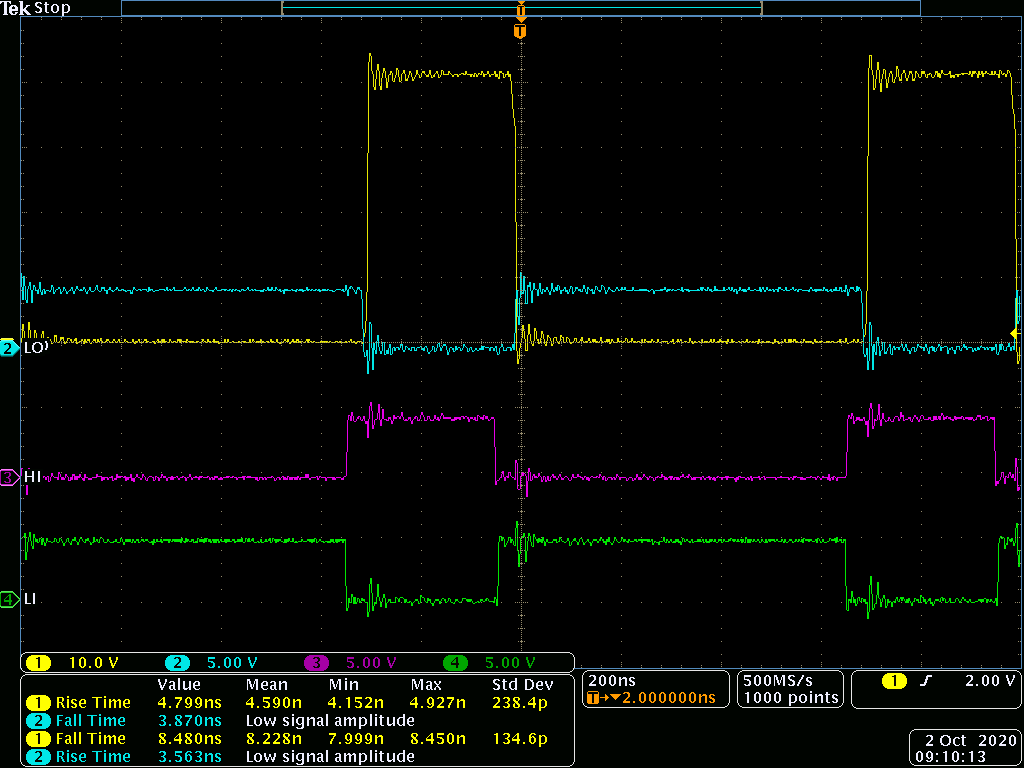

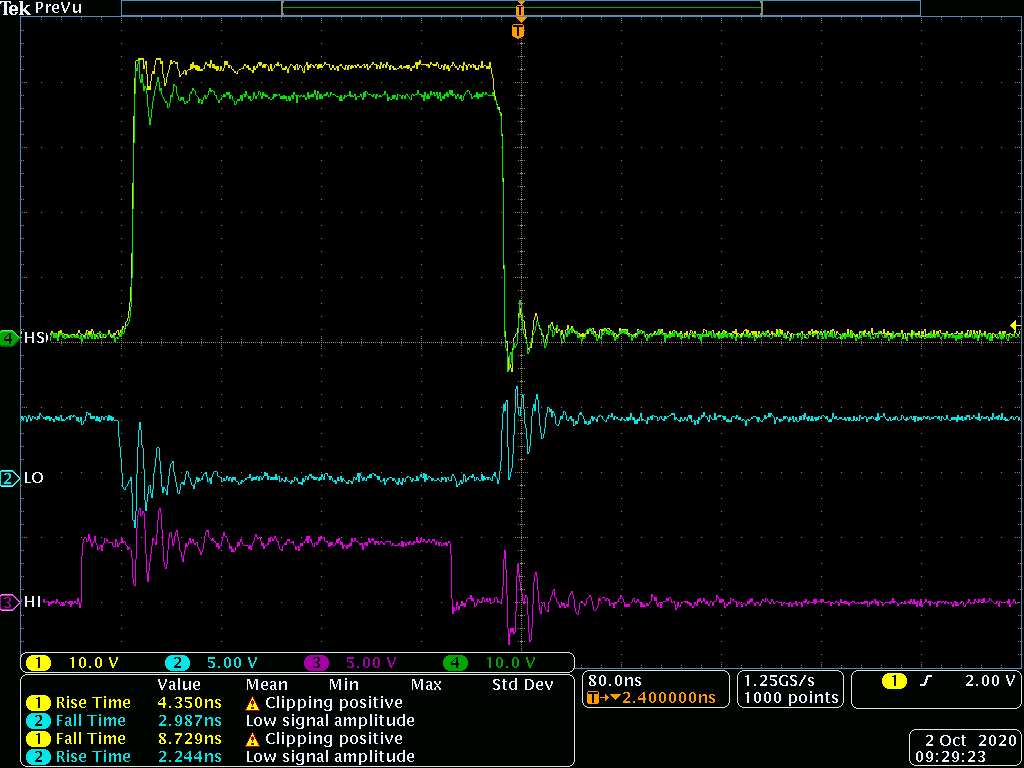

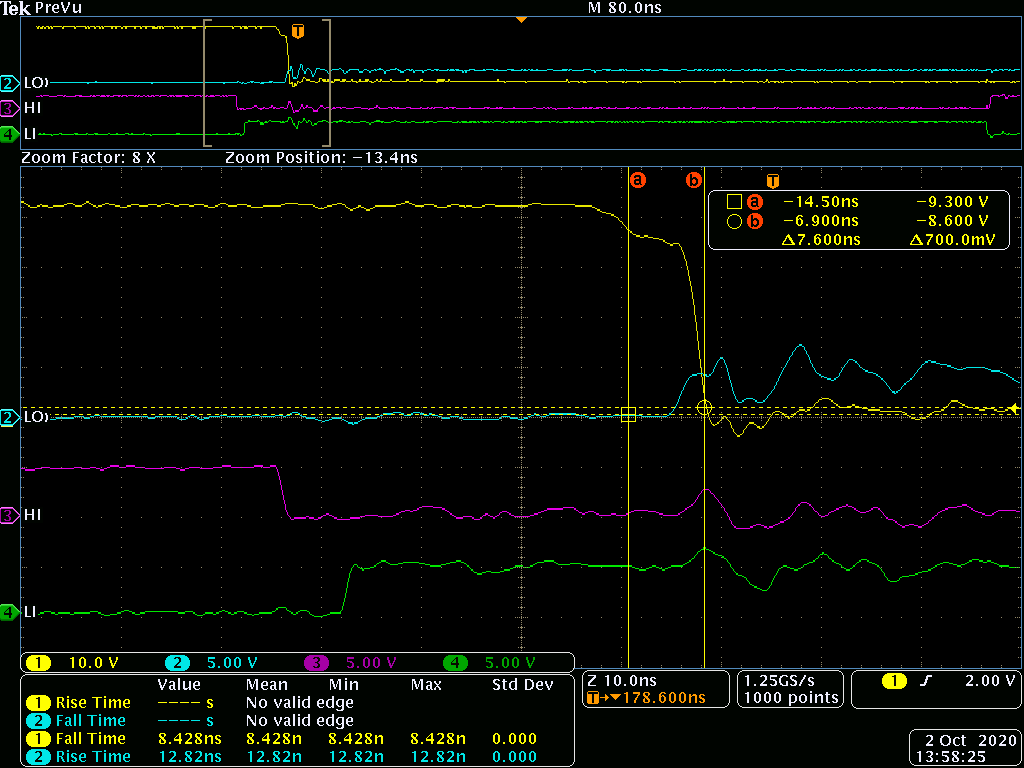

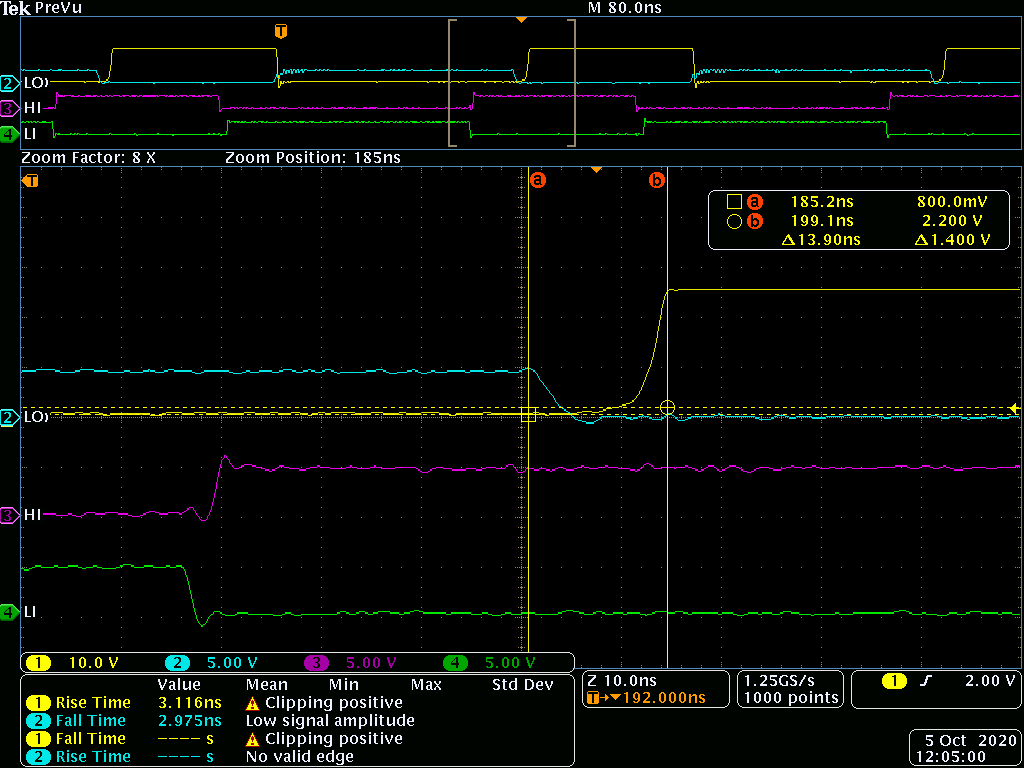

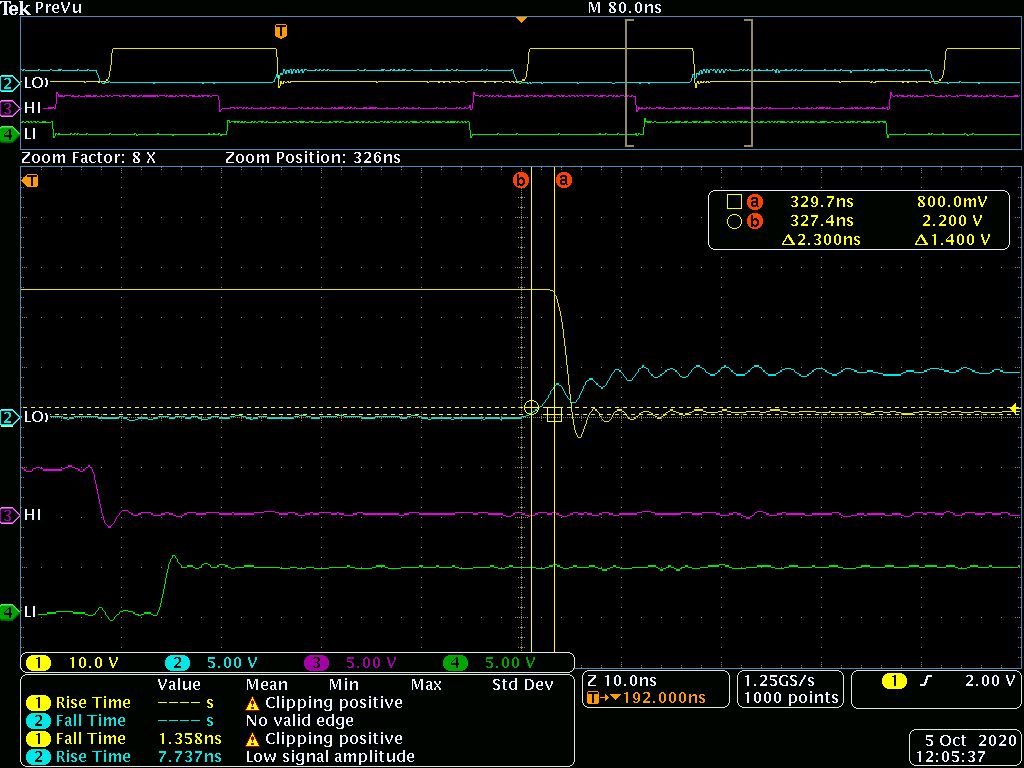

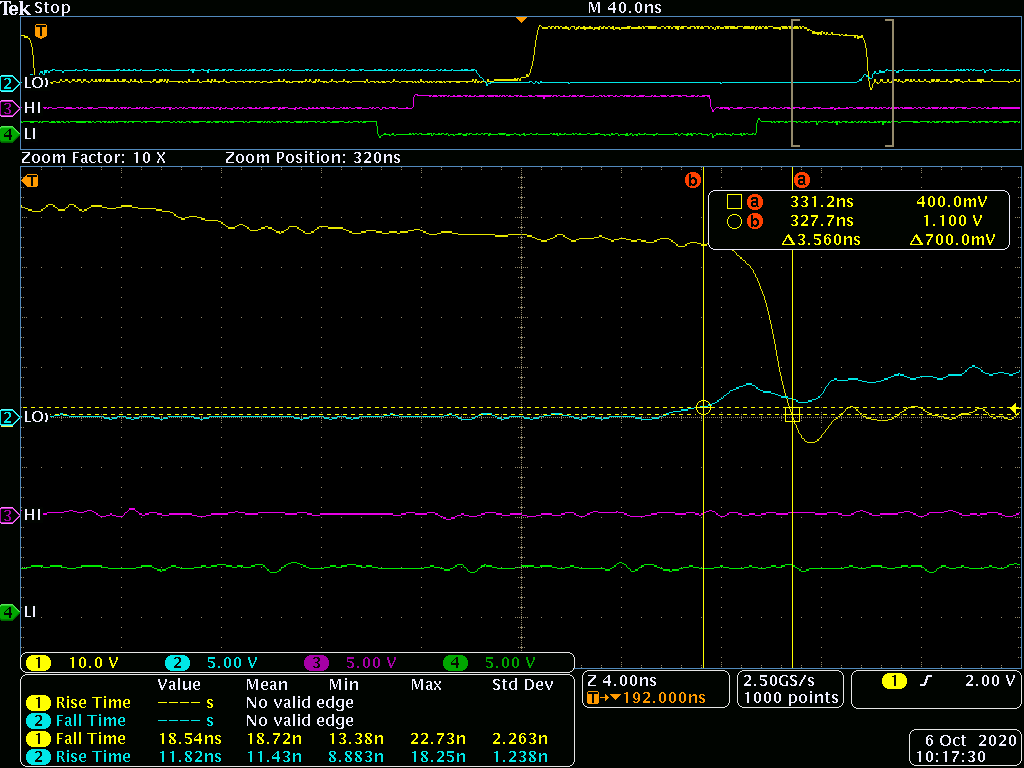

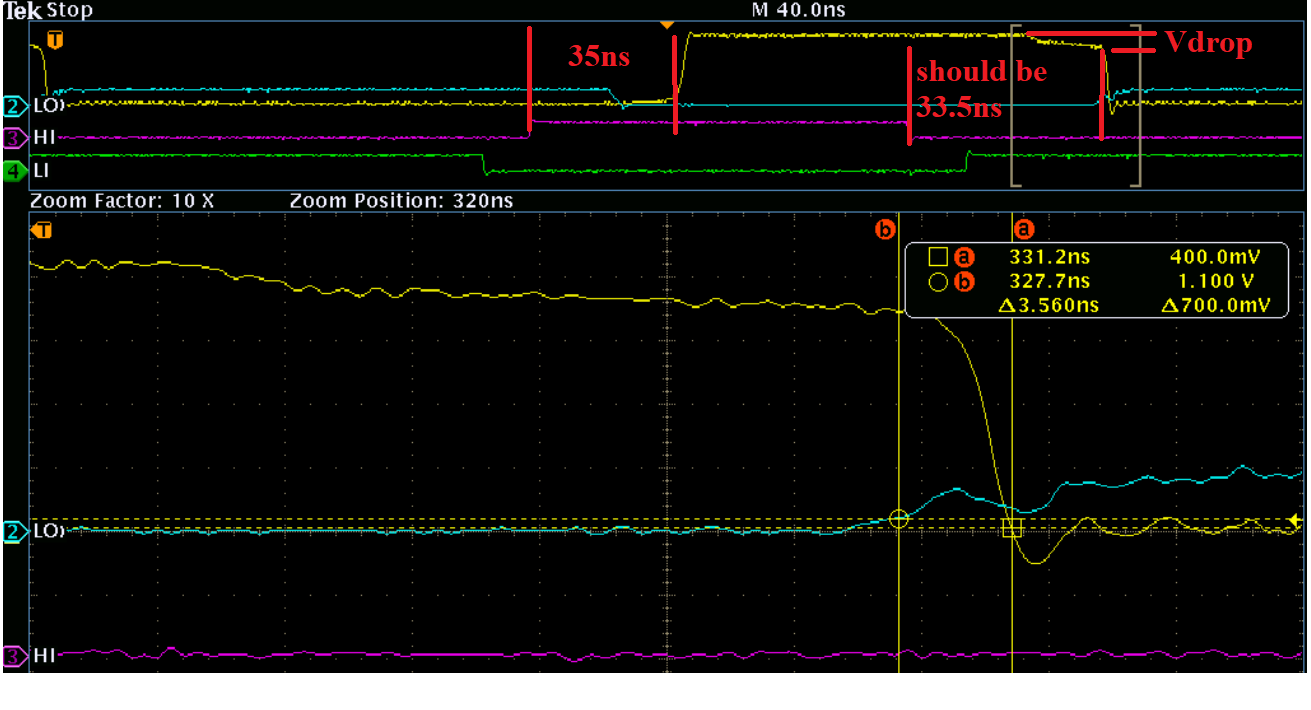

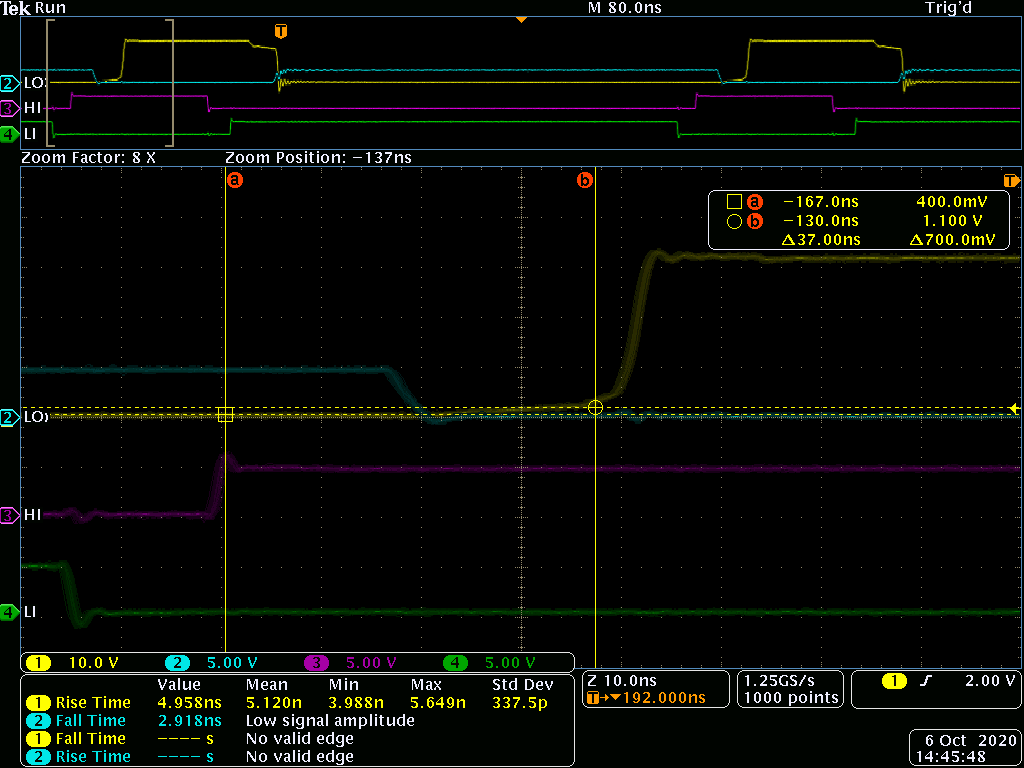

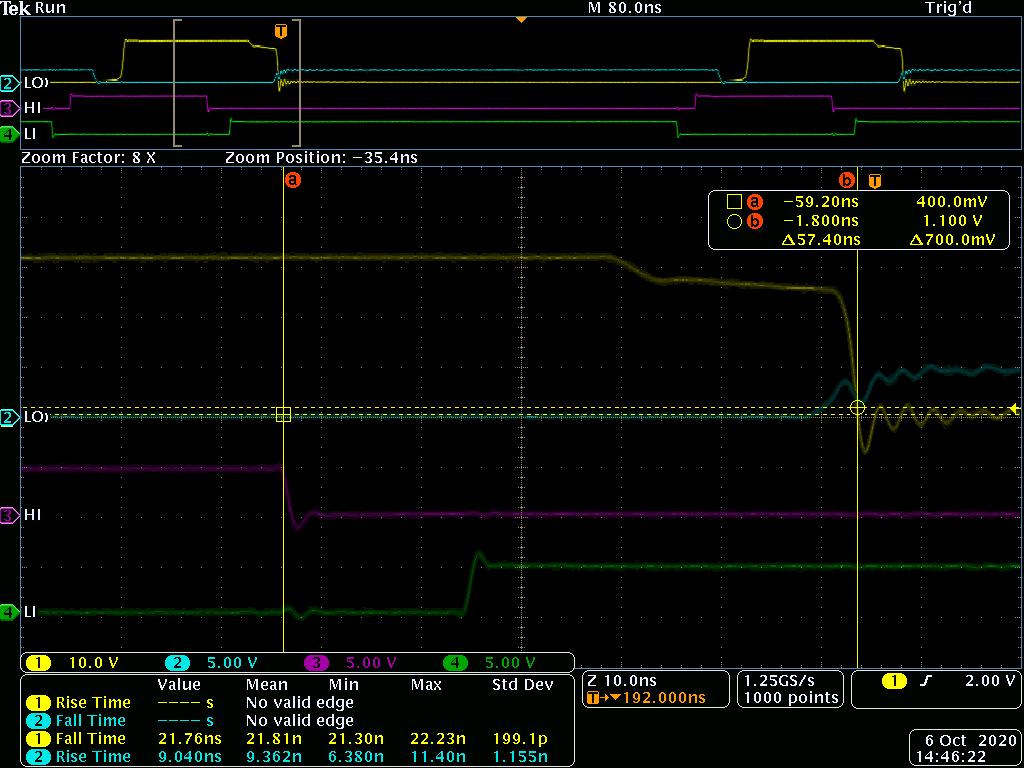

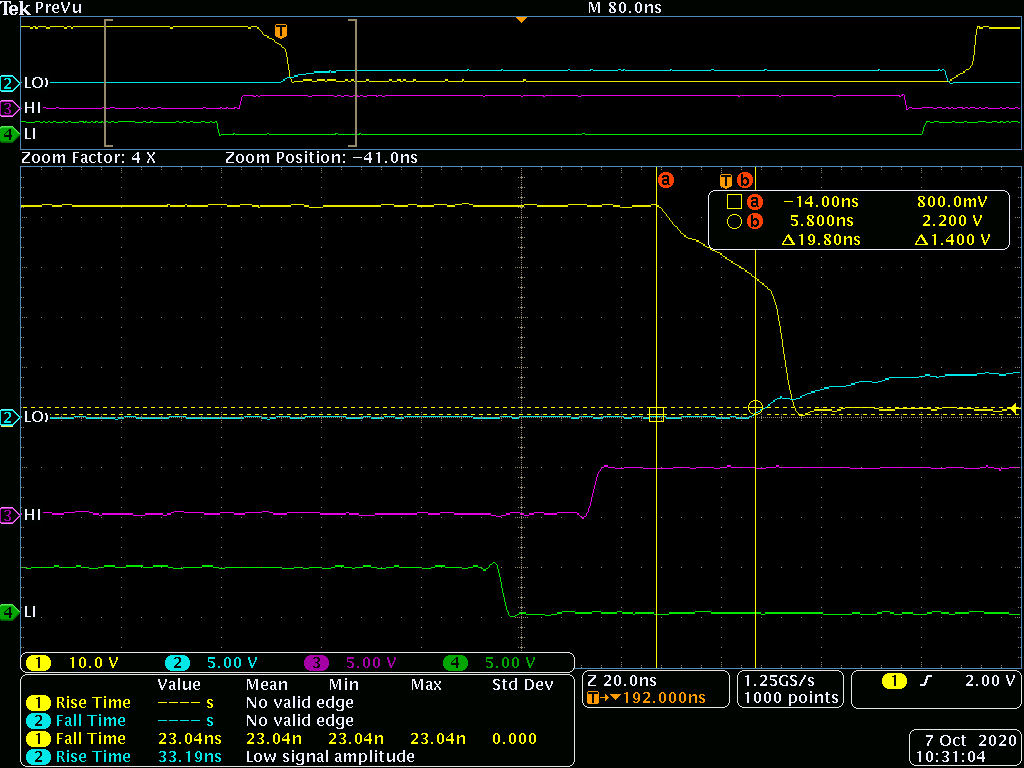

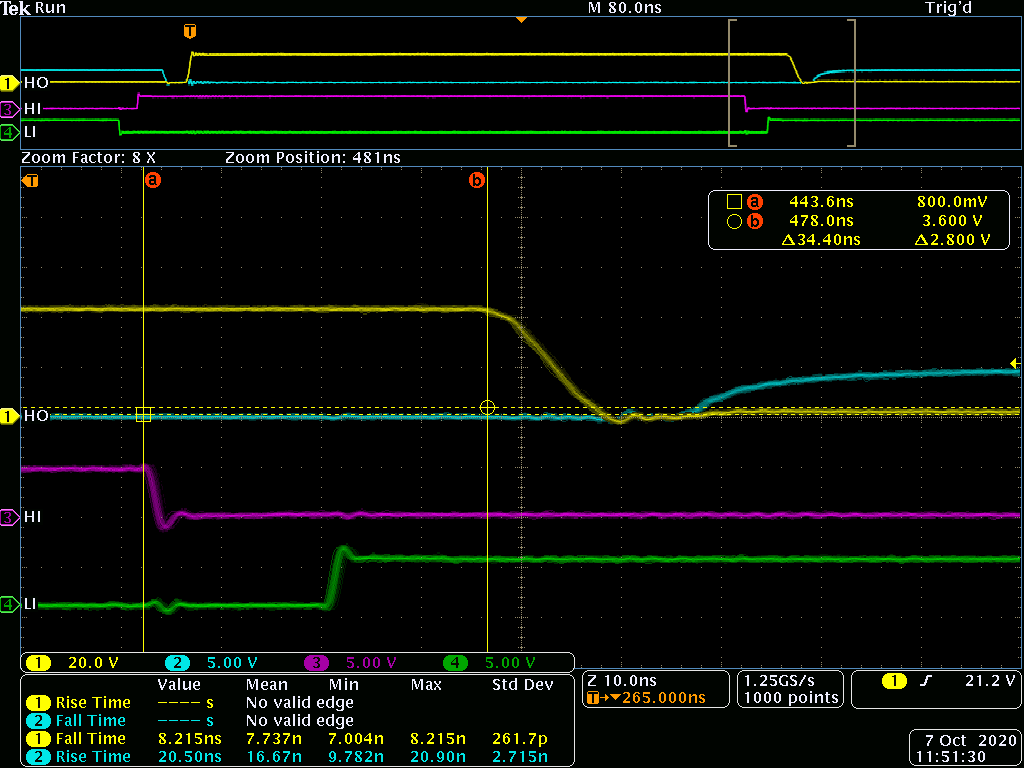

3- I calculate dead time on oscilloscope, with no load and without any Vbus. from HS fet-off to LS fet-on dead time is 1.5ns and from LS fet-off to HS fet-on dead time is 4ns, is it on the range? I didnt change anything on the kit LMG1205HBEVM.

4- How long we could work with no load on the LMG1205HBEVM, without any damaging the kit? like around 2 or 3 hours should damage it?

Thank you!