Hi SIR

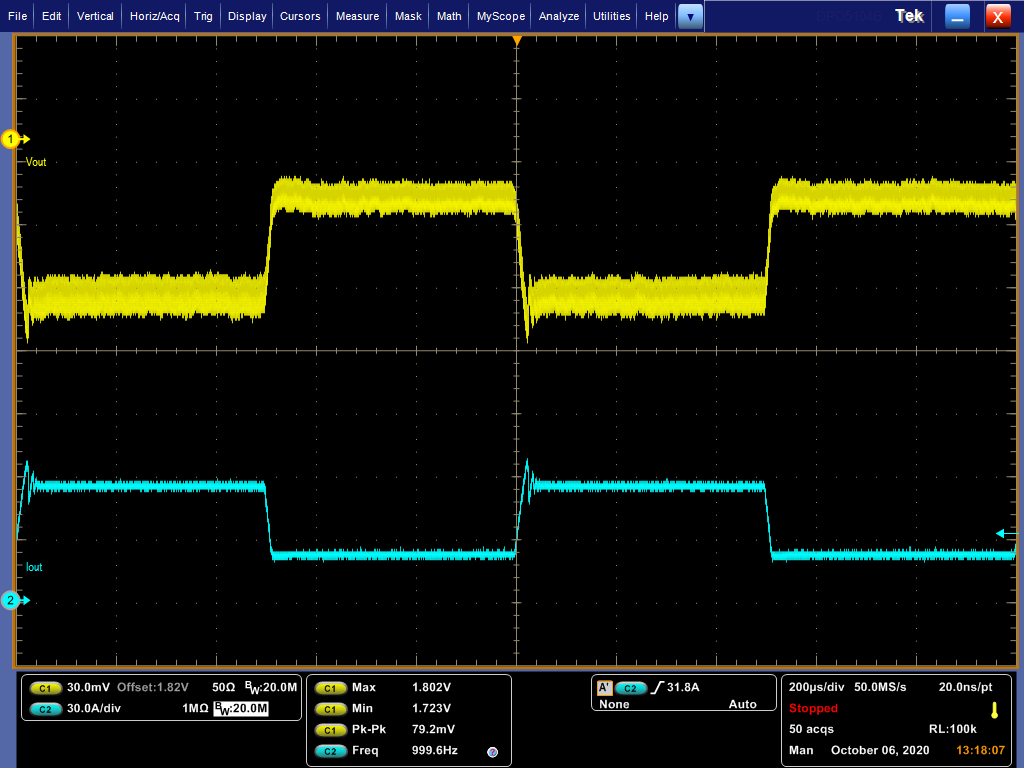

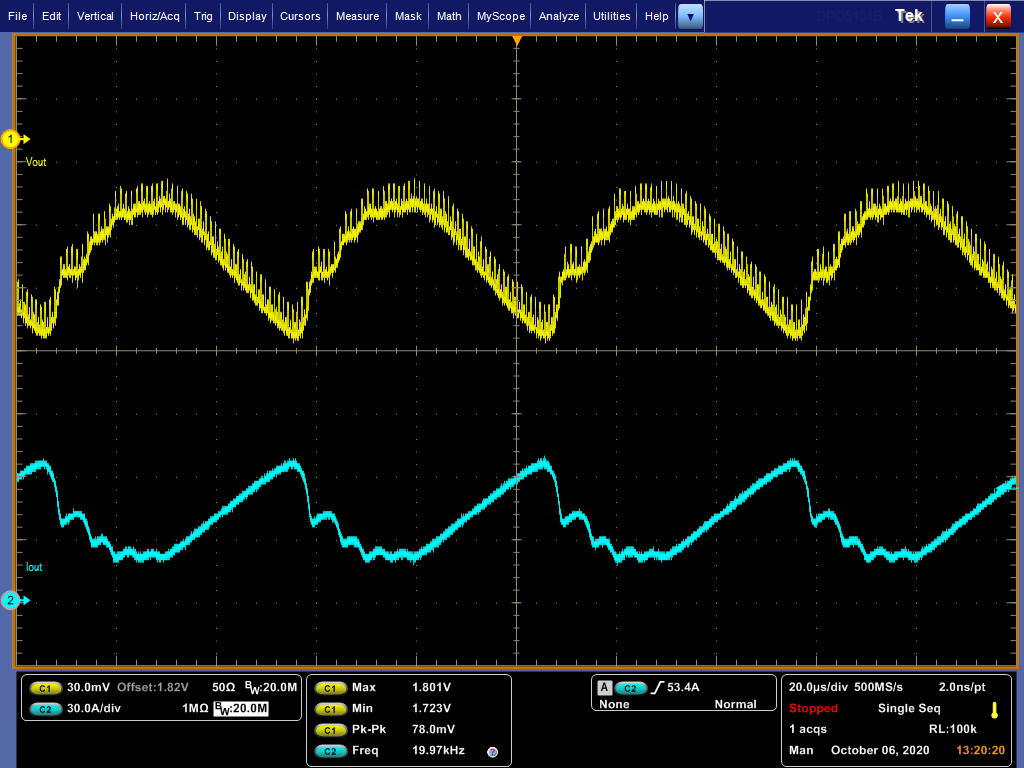

The circuit and Bode plot and POL Transient diagrams and specifications are as follows~~

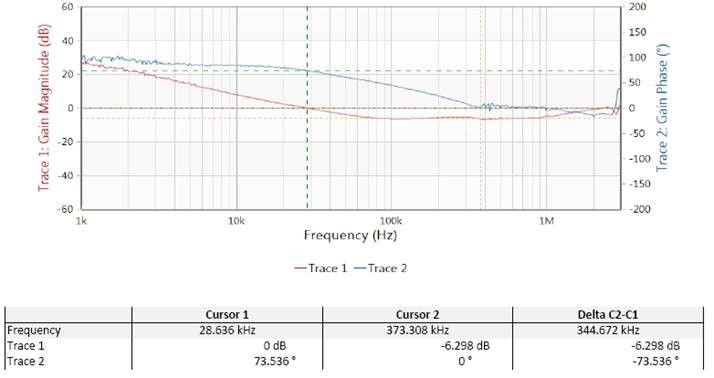

During the verification of VRTT and Bode plot , adjust the compensation parameters of the TPS53622 controller.

There are some challenges for both to meet specifications at the same time. The TPS53622 controller is adjusted to the best parameter values.

The best set of TPS53622 controller parameters are as follows.

AC_Gain : 2.0

AC_LL:2.375

INT_TIME:5

INT_GAIN:2.0

RAMP: 280mVp-p

If the CPU VRTT verification of the POL load side is passed, can the VRTT verification be used to replace the problem of BODE PLOT G.M. being less than -10dB?