Other Parts Discussed in Thread: UCC27282

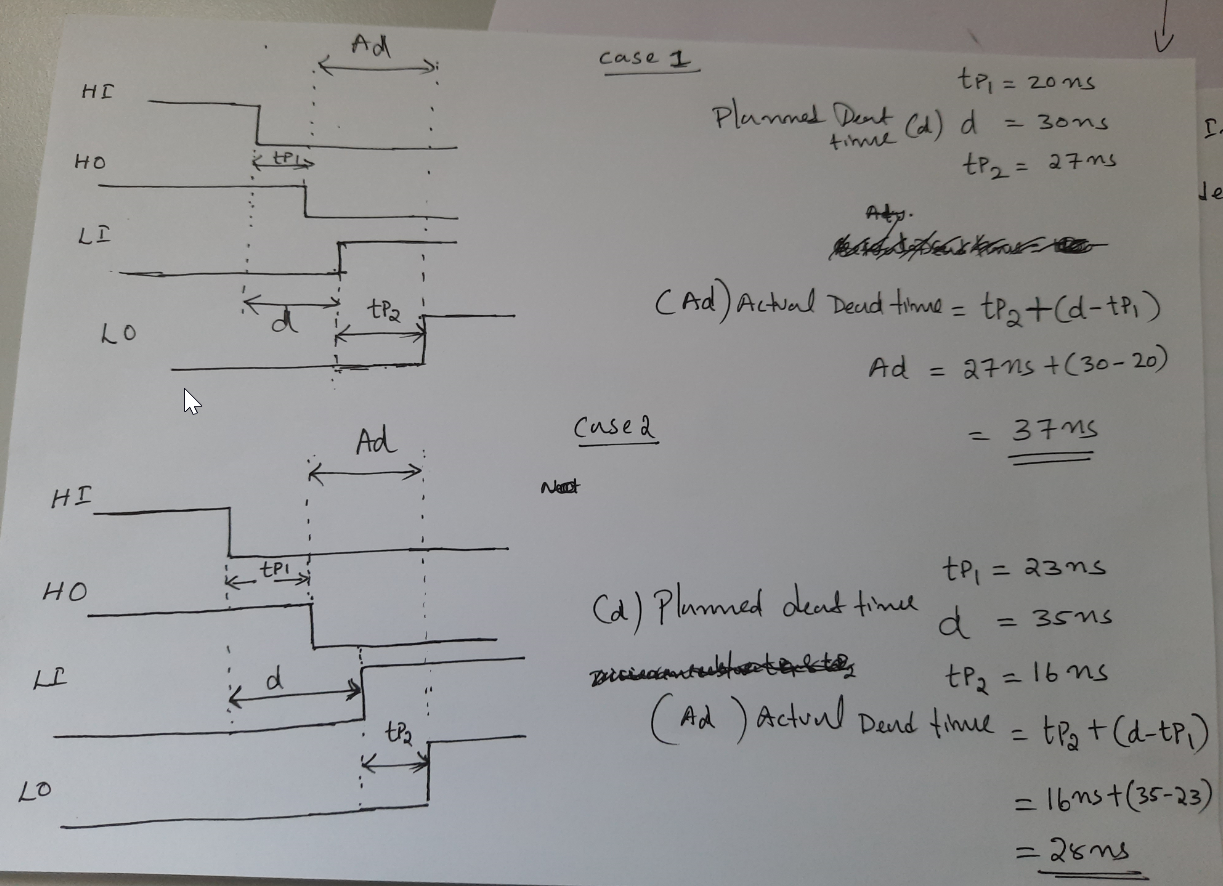

Delay Matching Time Understanding:

I have below questions, kindly answer all of them.

Is it a delay introduced by driver if their propagation delays between HI-HO and LI-LO are different ?

Is this value 0ns, if their propagation delays between HI-HO and LI-LO are matched ?

Is this value 0ns, if there is a deadtime between HI-HO and LI-LO more than 7ns ?

Regards,

kiran.