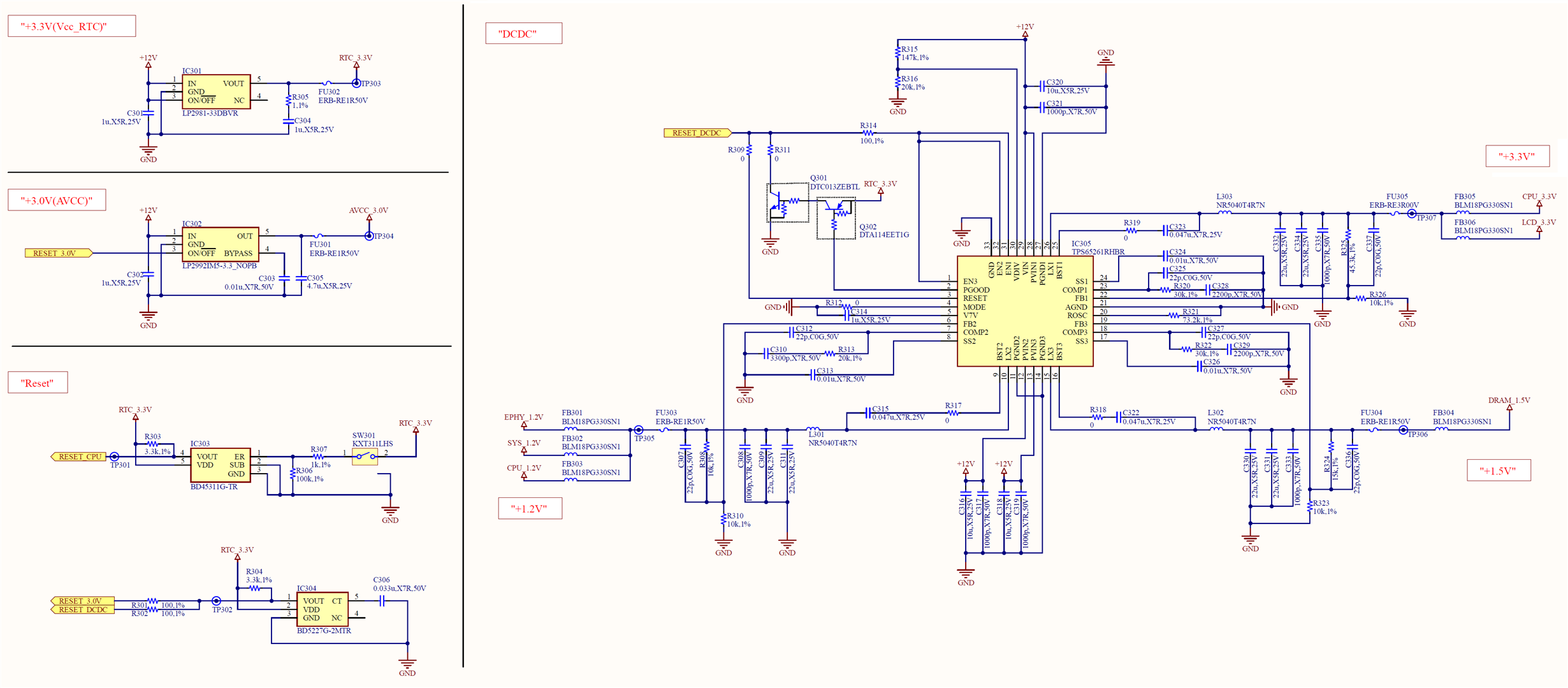

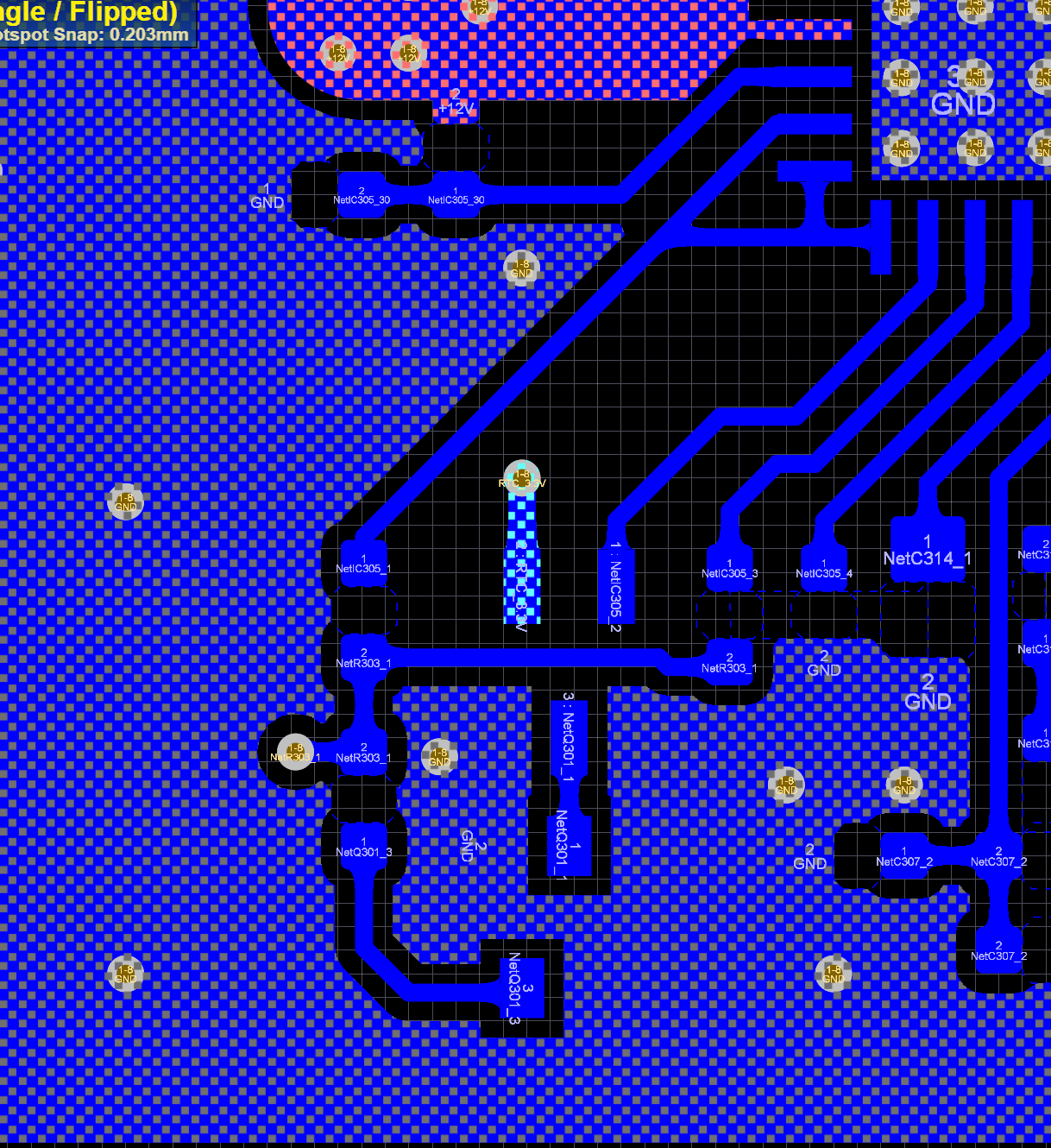

In the attached circuit.

R309 and R311 are not mounted.

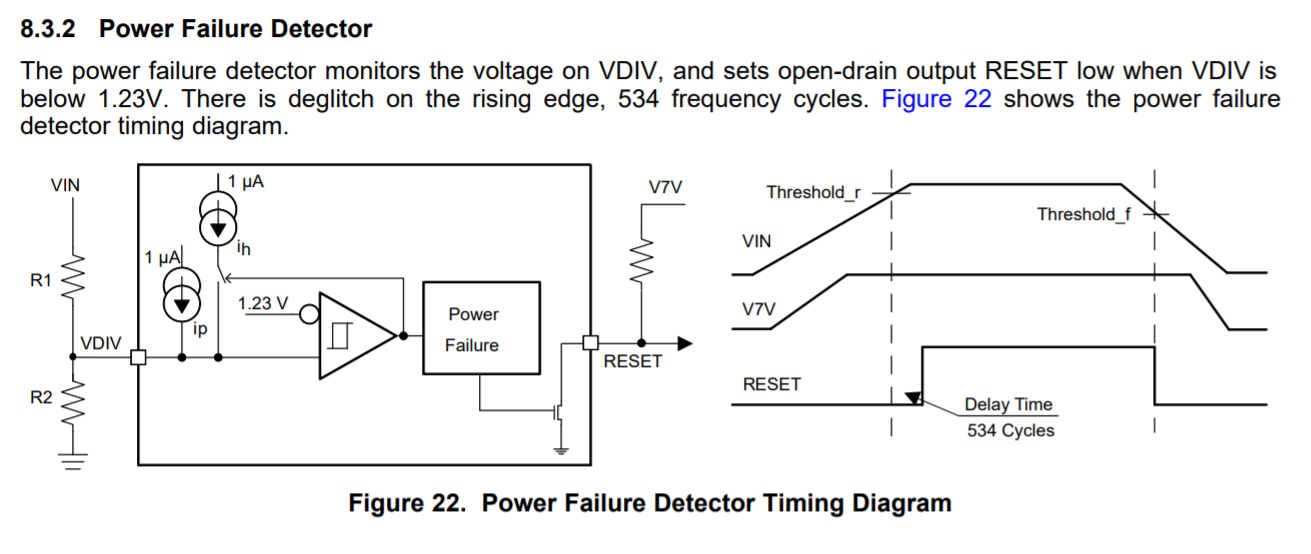

=> Signal "RESET_DCDC":H , TPS65261-2(PGOOD):H

R309 and R311 are mounted

=> Signal "RESET_DCDC":L , TPS65261-2(PGOOD):L

With R309 and R311 mounted, what should I change to make "PGOOD(pin2):H" and "RESET(pin3):H"?