Hi

I have an half bridge which is driven by LM5106.

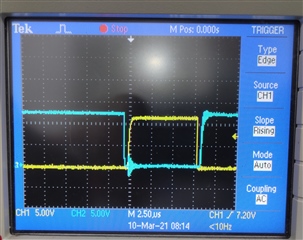

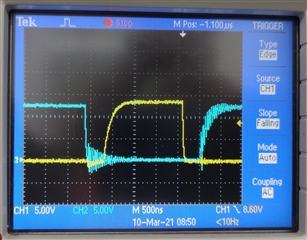

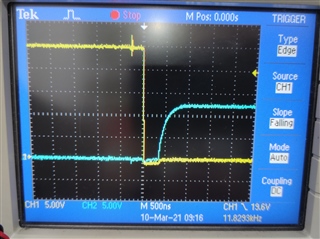

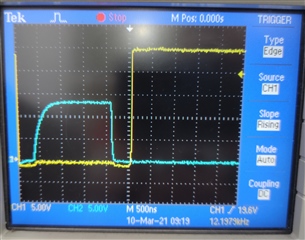

I have around 400nS dead time between high side and low side Vgs. But there is no effect of the this dead time at Vds for high side and low side mosfet.

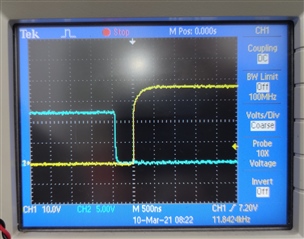

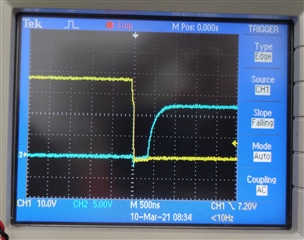

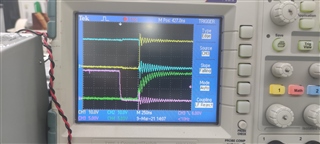

As you can see in the picture CH3 (Green) and CH4 (Purple) are Vgs high side and Vgs low side.

* the noise is because of the wiring to the oscilloscope *

CH1 (Yellow) is drain source voltage of the high side mosfet and CH2 (Blue) is drain source voltage of the low side mosfet.

even if I unplug the motor the signals are exactly the same.

this switching without dead time is happening in few nS but still effect on the DC line and motor current.

I already played with Rdt and increased the dead time but it is still the same Vds high side and low side change together.

the schematic is same with LM5106 schematic recommended in the datasheet

I need to know what is the reason of this problem that I have.