I have a question about the ISET terminal of BQ24171RGYT.

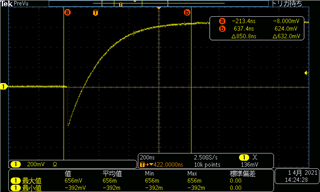

The "BQ24171RGYT" charging current setting terminal (ISET terminal) is switched from 0V to 120mV or more using FET, but once it is changed from 0V to 120mV or more, the voltage drops to around -400mV.

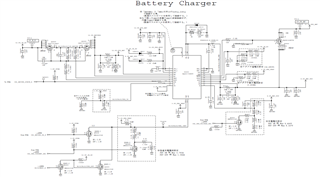

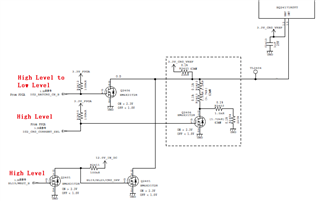

The schematic and waveform are attached.

CH1:ISET

It seems that BQ24171RGY is pulling to -400mV.

Isn't there such a thing?

The maximum rating of the ISET terminal is stated as -0.3V in the data sheet. Is the maximum rating of the ISET terminal really -0.3V?

Please answer.